**ESMT FE8116x**

**Technical Reference**

**Manual**

Revision: V0.1 Date: October 15,

2022

## TABLE OF CONTENTS

|       |                                                          |     |

|-------|----------------------------------------------------------|-----|

| 1     | GENERAL DESCRIPTION.....                                 | 5   |

| 2     | FEATURES                                                 |     |

| 2.1   | FE81 Series Features .....                               | 6   |

| 3     | PARTS INFORMATION LIST                                   |     |

| 3.1   | ESMT FE81 Series Selection Guide.....                    | 10  |

| 4     | PIN CONFIGURATION .....                                  | 11  |

| 5     | BLOCK DIAGRAM                                            |     |

| 5.1   | ESMT FE81 Series Block Diagram.....                      | 12  |

| 6     | BLOCK FUNCTIONAL DESCRIPTION                             |     |

| 6.2   | Memory Organization                                      |     |

| 6.2.1 | FE81 Series Memory Map .....                             | 15  |

| 6.3   | External Vectored Interrupt Controller (EVIC)            |     |

| 6.3.1 | Overview.....                                            | 21  |

| 6.3.2 | FE81 Series Interrupt Entry Point and Interrupt Map..... | 22  |

| 6.3.3 | FE81 Series Interrupt Priority .....                     | 23  |

| 6.3.4 | External Interrupt .....                                 | 25  |

| 6.3.5 | Register Map and Description.....                        | 26  |

| 6.4   | System Manager Controller (SMU)                          |     |

| 6.4.1 | Overview.....                                            | 36  |

| 6.4.2 | Reset Control .....                                      | 37  |

| 6.4.3 | General Purpose I/O .....                                | 39  |

| 6.4.4 | Register Map and Description.....                        | 40  |

| 6.5   | Clock Controller (CLKCTRL)                               |     |

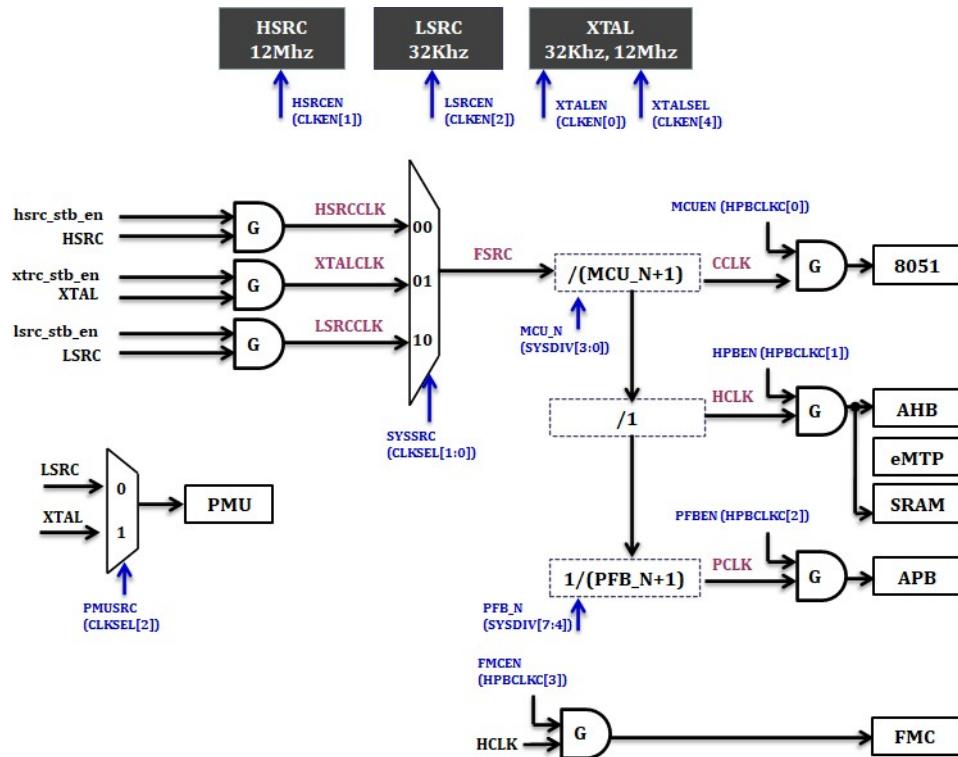

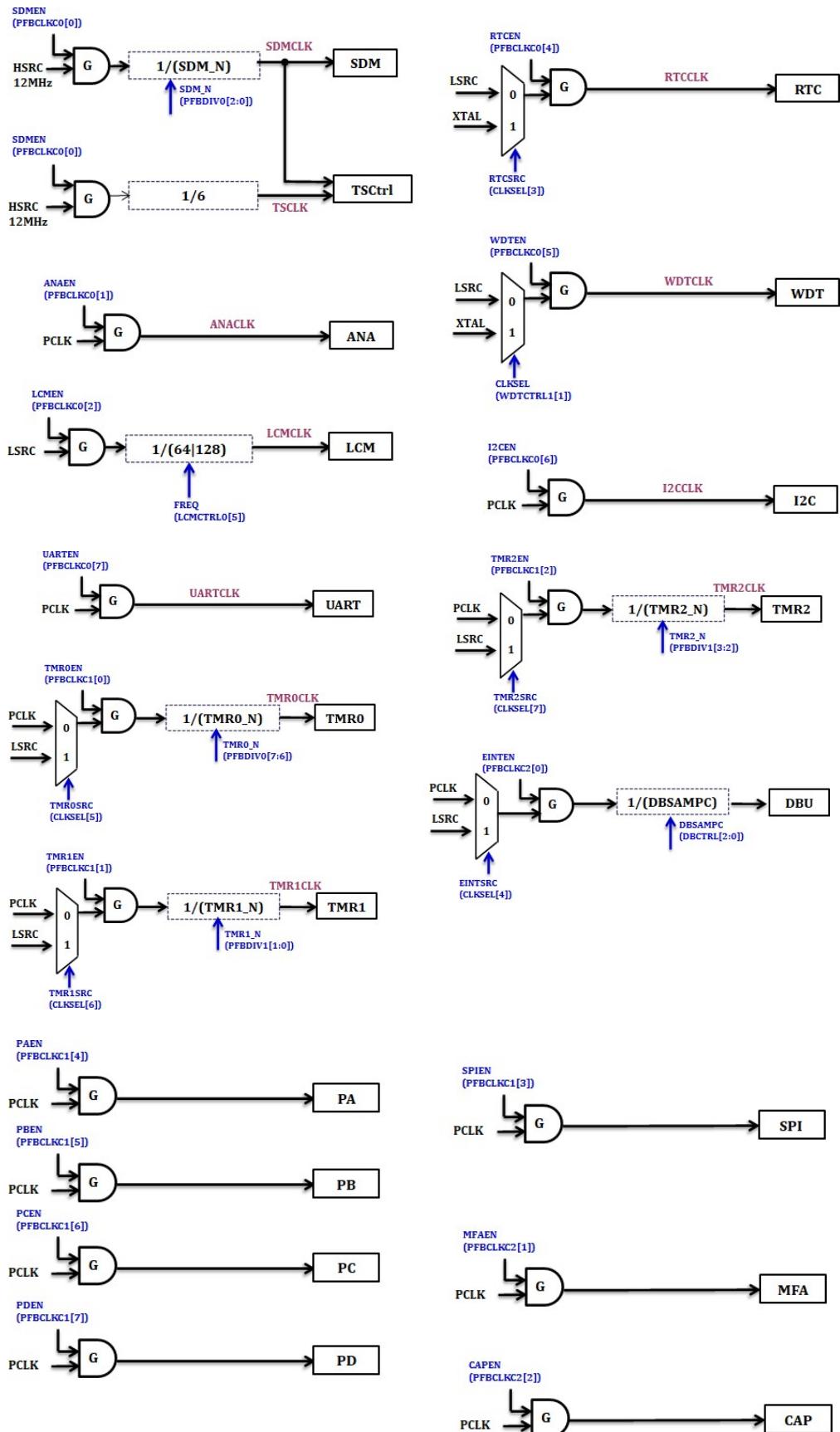

| 6.5.1 | Overview .....                                           | 77  |

| 6.5.2 | Clock Plan Block Diagram.....                            | 78  |

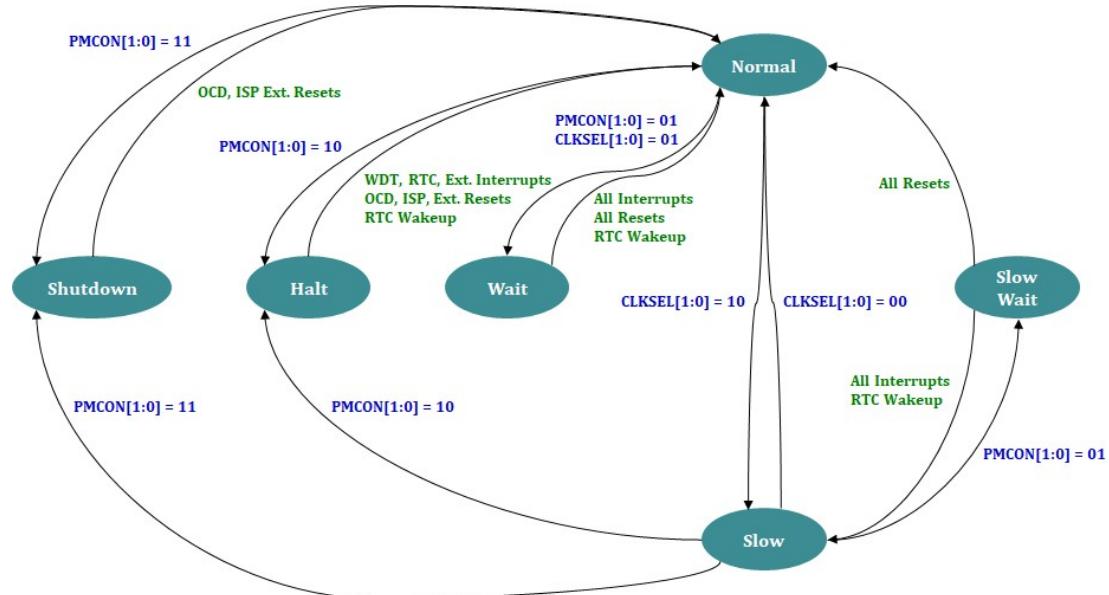

| 6.5.3 | Low Power Mode... .....                                  | 80  |

| 6.5.4 | Register Map and Description.....                        | 83  |

| 6.6   | Flash Memory Controller (FMC)                            |     |

| 6.6.1 | Overview .....                                           | 96  |

| 6.6.2 | System Configuration .....                               | 98  |

| 6.6.3 | Debug Access Port (DAP).....                             | 100 |

| 6.6.4 | In-System-Programming (ISP).....                         | 101 |

| 6.6.5 | Register Map and Description.....                        | 102 |

| 6.7   | Sigma-Delta ADC (SDM)                                    |     |

| 6.7.1 | Overview .....                                           | 112 |

---

|        |                                              |     |

|--------|----------------------------------------------|-----|

| 6.7.2  | Register Map and Description.....            | 113 |

| 6.8    | Analog Controller (ANAC)                     |     |

| 6.8.1  | Overview .....                               | 131 |

| 6.8.2  | Register Map and Description.....            | 132 |

| 6.9    | Real-Time Clock (RTC)                        |     |

| 6.9.1  | Overview.....                                | 143 |

| 6.9.2  | Register Map and Description.....            | 144 |

| 6.9.3  | Programming Model .....                      | 155 |

| 6.10   | Watchdog Timer Controller (WDT)              |     |

| 6.10.1 | Overview .....                               | 157 |

| 6.10.2 | Register Map and Description.....            | 159 |

| 6.10.3 | Programming Model.....                       | 165 |

| 6.11   | Timer Controller (TMR)                       |     |

| 6.11.1 | Overview. ....                               | 166 |

| 6.11.2 | Register Map and Description. ....           | 168 |

| 6.11.3 | Programming Model. ....                      | 179 |

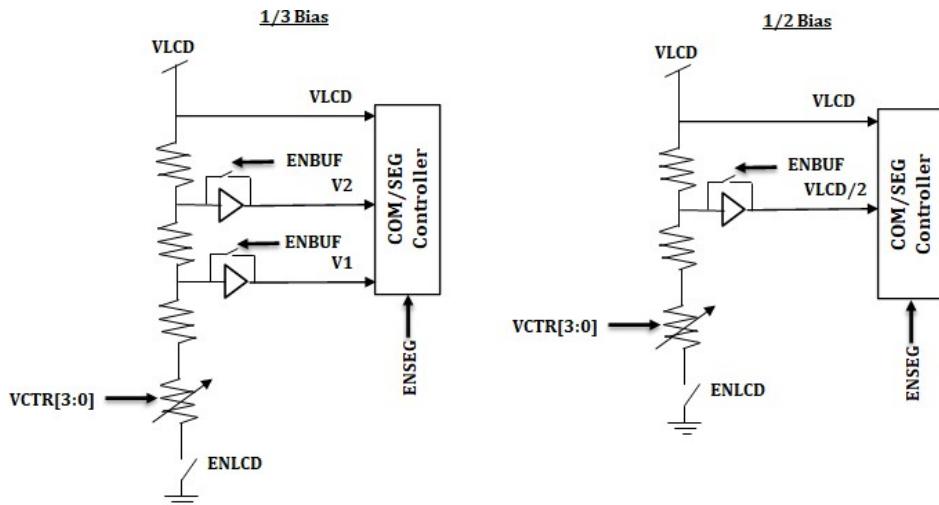

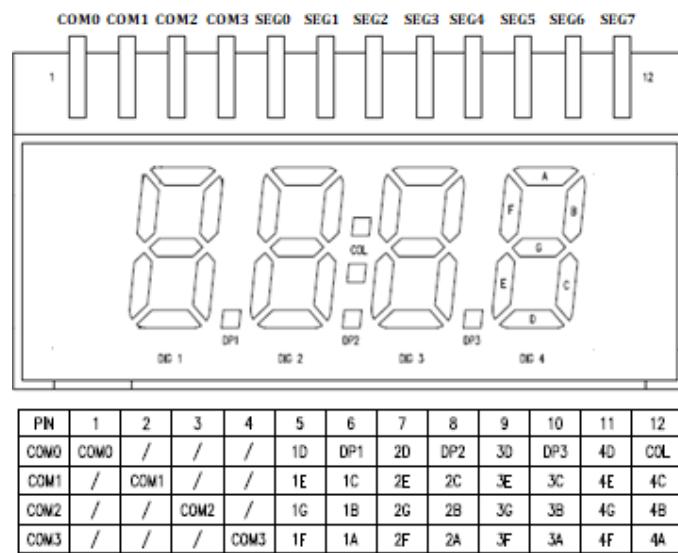

| 6.12   | STN LCD Controller (LCM)                     |     |

| 6.12.1 | Overview. ....                               | 181 |

| 6.12.2 | Register Map and Description.....            | 184 |

| 6.12.3 | Programming Model. ....                      | 188 |

| 6.13   | I2C Serial Interface Controller (I2C)        |     |

| 6.13.1 | Overview.....                                | 189 |

| 6.13.2 | Register Map and Description.....            | 191 |

| 6.13.3 | Programming Model.....                       | 207 |

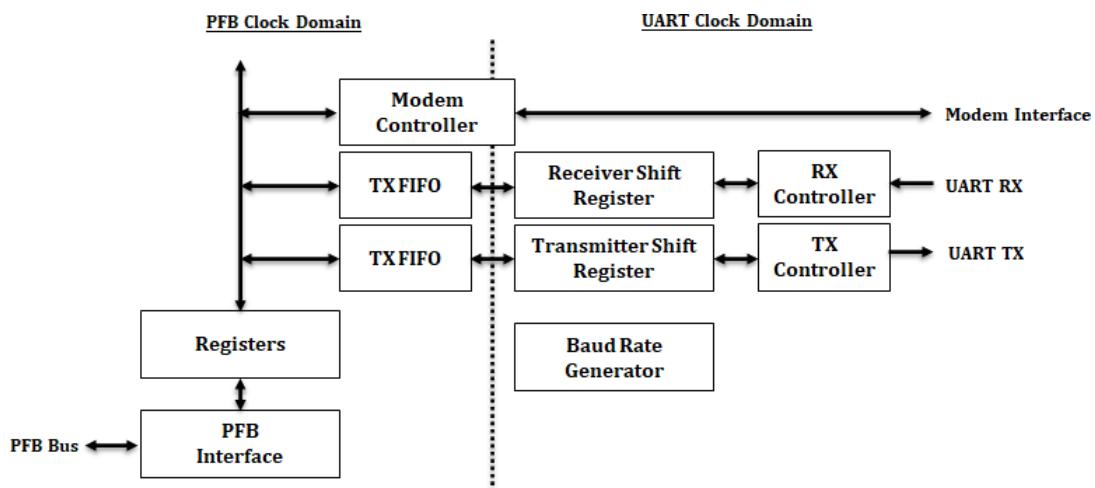

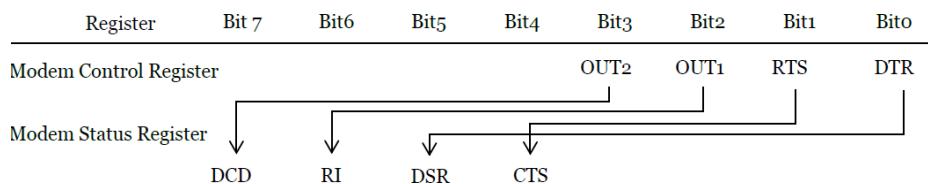

| 6.14   | UART Interface Controller (UART)             |     |

| 6.14.1 | Overview. ....                               | 211 |

| 6.14.2 | Register Map and Description. ....           | 215 |

| 6.14.3 | Programming Model. ....                      | 226 |

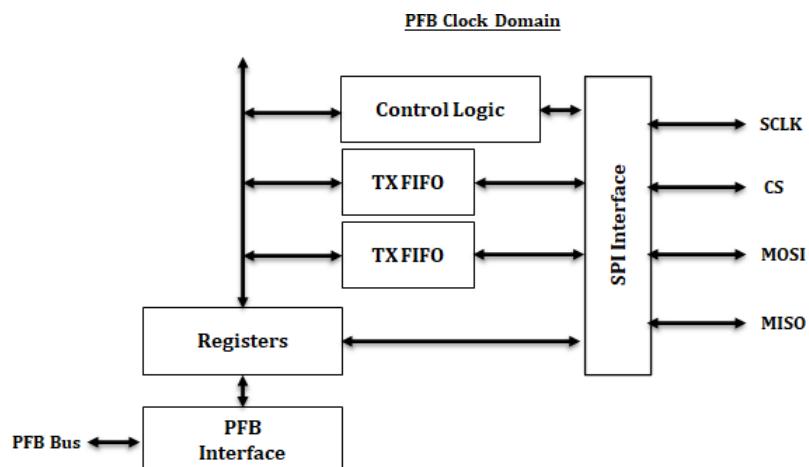

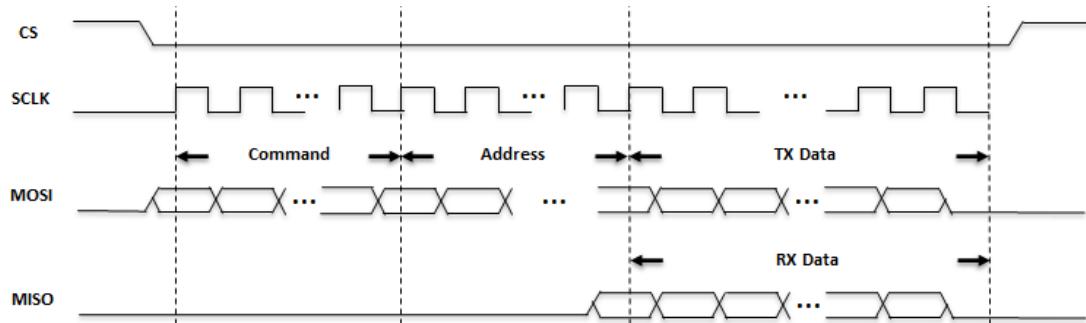

| 6.15   | Serial Peripheral Interface Controller (SPI) |     |

| 6.15.1 | Overview. ....                               | 227 |

| 6.15.2 | Register Map and Description. ....           | 230 |

| 6.15.3 | Programming Model. ....                      | 257 |

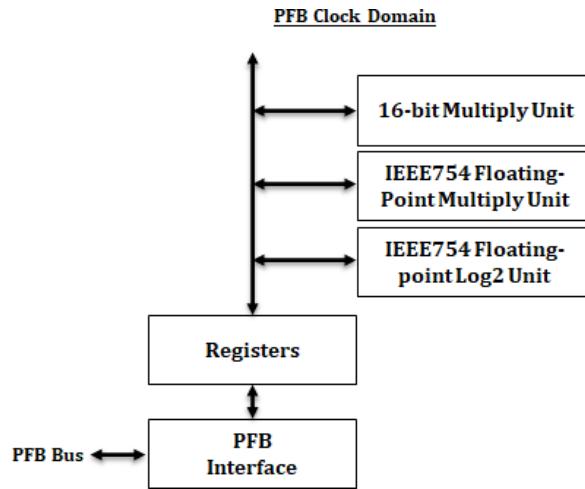

| 6.16   | Multi-Function ALU (MFA)                     |     |

| 6.16.1 | Overview. ....                               | 259 |

| 6.16.2 | Register Map and Description.....            | 260 |

| 6.16.3 | Programming Model. ....                      | 272 |

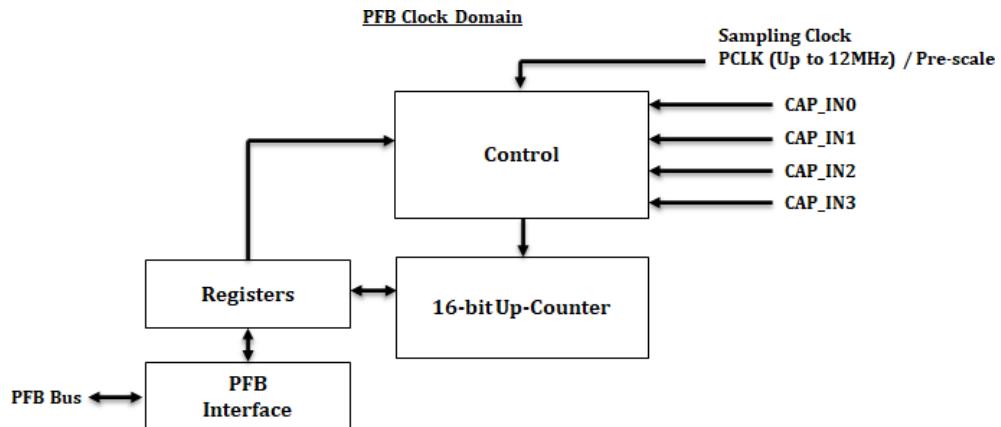

| 6.17   | Capture (CAP)                                |     |

| 6.17.1 | Overview.....                                | 275 |

---

---

|        |                                   |     |

|--------|-----------------------------------|-----|

| 6.17.2 | Register Map and Description..... | 277 |

| 6.17.3 | Programming Model. ....           | 285 |

## 1 GENERAL DESCRIPTION

ESMT FE81 series is a general purpose 8051 platform that targets on various consumer applications. The MCU platform is integrated with an 8051 core running up to 12MHz, up to 8K-byte eMTP flash memory, and up to 1K-byte data SRAM (X-RAM) with 256-byte internal-SRAM (I-RAM). The MCU platform is also integrated with rich peripherals support, including real-time clock (RTC), watchdog timer controller (WDT), timer controller (TMR), UART interface controller (UART), I2C serial interface controller (I2C), serial peripheral interface controller (SPI), 24-bit high resolution delta-sigma ADC (SDM), analog controller (ANAC), STN LCD driver (LCM), and multi-function ALU (MFA).

ESMT FE81 series supports 2.2V ~ 3.6V voltage range. The operation temperature is from -40°C ~ 125 °C.

| Part   | RTC | WDT | TMR | UART | I2C | SPI | SDM | ANAC | LCM | MFA | CAP |

|--------|-----|-----|-----|------|-----|-----|-----|------|-----|-----|-----|

| FE81XX | 1   | 1   | 3   | 1    | 1   | 1   | 1   | 1    | 1   | 1   | 1   |

Table 1-1 Peripheral Table

## 2 FEATURES

### 2.1 FE81 Series Features

- 8-bit Micro-controller

- 8051 core runs up to 12MHz@2.9V~3.6V

- 8051 core runs up to 3MHz@1.8V~2.9V

- 1-T architecture with extensive clock-gating

- Compatible 8051 instruction format

- Single-cycle 8-bit hardware multiplier

- 2-wire ICE debugger interface ESMT-SWD

- ◆ 8 hardware breakpoints support

- ◆ Memory subsystems and all peripherals access

- Synchronous high-performance bus (HPB) for memory subsystems

- Synchronous peripheral bus (PFB) for all peripherals

- Embedded RAM

- 1 x 256-byte Internal I-RAM for application data storage

- 1 x 1K-byte single port SRAM (X-RAM) for application data storage

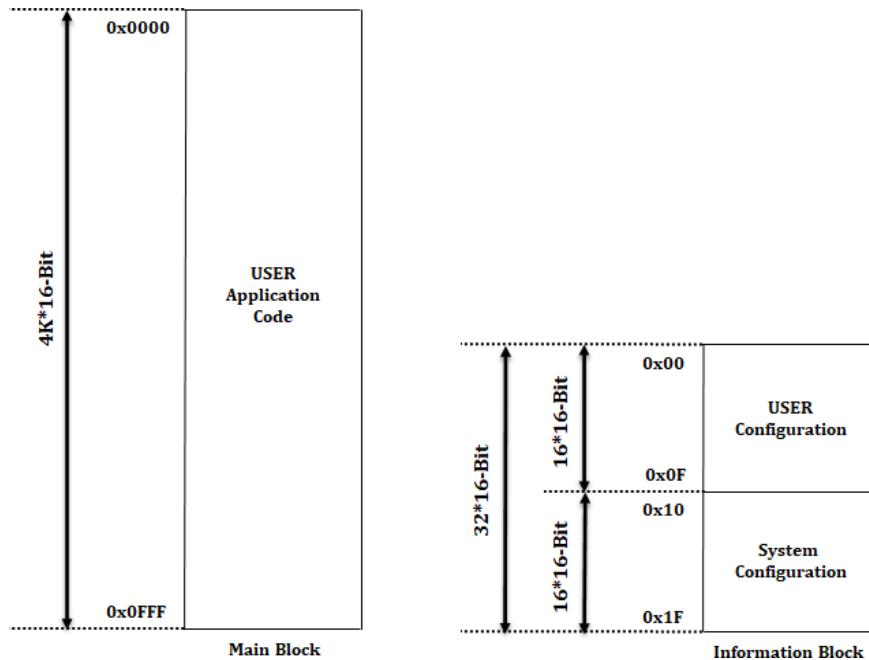

- Flash Memory

- 8K-byte eMTP flash for application code

- 32-byte information eMTP flash for system configuration parameters

- 32-byte information eMTP flash for customer data storage

- Advanced Power Management

- Various low power mode including slow, wait, slow wait, halt, and shutdown modes

- External interrupt, reset, and peripheral wake-up mechanism

- System Manager Controller (SMU)

- Part number identification

- Reset control mechanism

- General purpose I/O control mechanism

- Timer additional control mechanism

- SRAM parameter configuration control

- Clock Controller (CLKC)

- High-performance bus (HPB) clock control mechanism

- Peripheral bus (PFB) clock control mechanism

- Clock selection control mechanism

- Clock division control mechanism

- Power down control mechanism

- External Vector interrupt controller (EVIC)

- 16 hardware vector interrupt signals

- Fixed priority level triggered interrupt mechanism

- Global interrupt enable for nested interrupt selection

- Edge triggered type of external interrupt

- Flash Memory Controller (FMC)

- Application code eMTP flash memory access

- System configuration information eMTP flash memory access

- Customer data information eMTP flash memory access

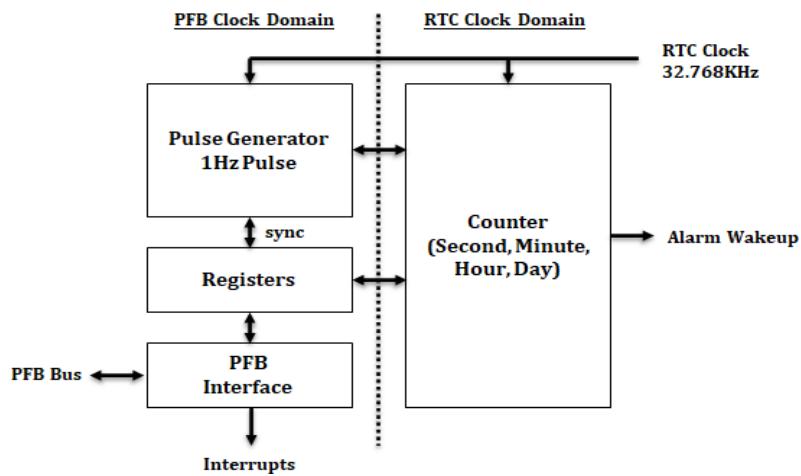

- Real-Time Clock (RTC)

- Second, minute, hour, day for periodic interrupts

- Programmable alarm support

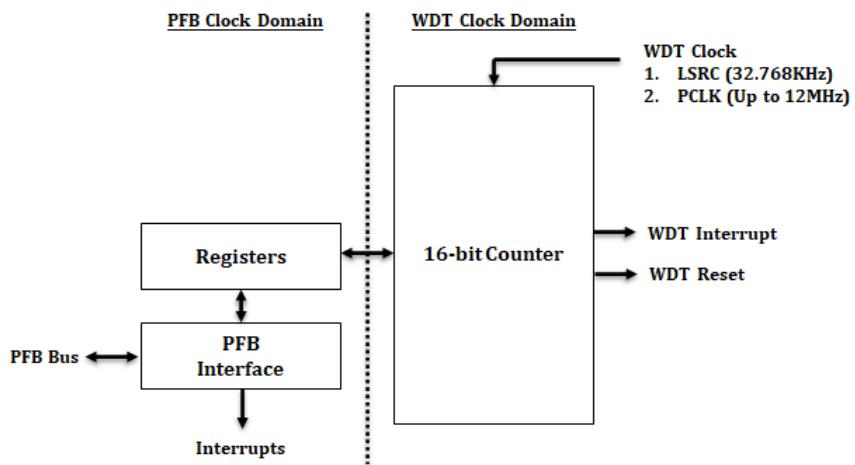

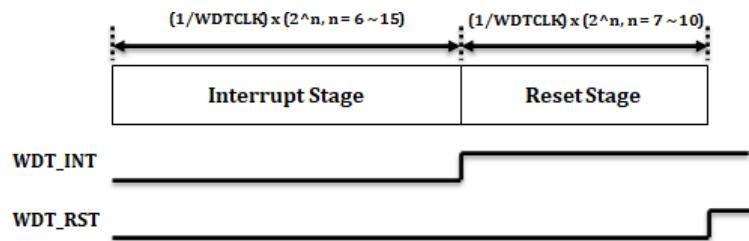

- Watchdog Timer Controller (WDT)

- Provide combinations of interrupt and reset when the watchdog timer expires

- Provide a write protection mechanism for the control or restart registers

- Programmable source of timer clock

- Configurable magic numbers for write protection of registers and restart of the timer

- Externally Watchdog timer be paused by FMC controller

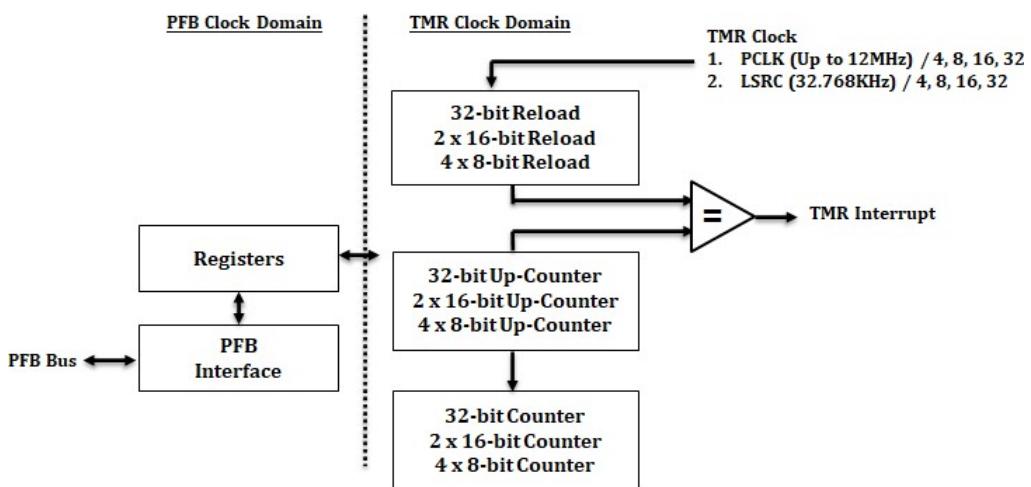

- Timer Controller (TMR)

- 3 timer controllers

- Each Timer

- ◆ Each timer has 2-channel

- ◆ Each channel supports 6 multi-function timers

- 32-bit Timer / 2 16-bit Timers / 4 8-bit Timers / PWM / PWM+16-bit Timer / PWM+8-bit Timers

- Programmable source of timer clock

- Timers can be externally paused by SMU controller

- UART Interface Controller (UART)

- 1 UART interface controller

- Over-sampling frequency is programmable

- Support 5 to 8 bits per character

- Support 1, 1.5, 2 STOP bits

- Support even, odd and stick parity bits

- Support programmable baud rate

- 16-byte hardware transmit or receive FIFOs

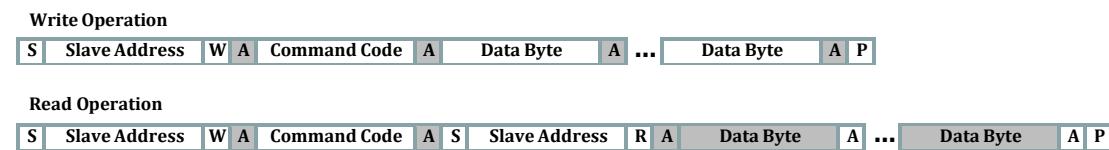

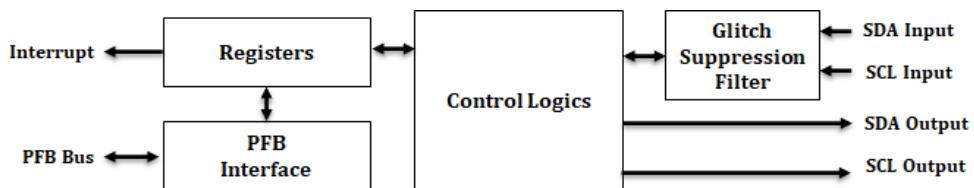

- I2C Serial Interface Controller (I2C)

- 1 I2C serial interface controllers

- Support standard-mode (100Kb/s), fast-mode (400Kb/s), and fast-mode plus (1Mb/s)

- protocols

- Programmable master or slave mode

- Support 7-bit and 10-bit addressing mode

- Support general call address

- Auto clock stretching

- Programmable clock or data timing

- 8-byte hardware transmit or receive FIFOs

- Serial Peripheral Interface Controller (SPI)

- 1 serial peripheral interface controllers

- Support MSB or LSB first transfer

- Support programmable SPI SCLK

- Programmable master or slave mode

- ◆ SPI Master maximum@6MHz with PFB clock 12MHz

- ◆ SPI Slave maximum@3MHz with PFB clock 12MHz

- Support 8- or 16- or 24-bit address bus

- 8-byte hardware transmit or receive FIFOs

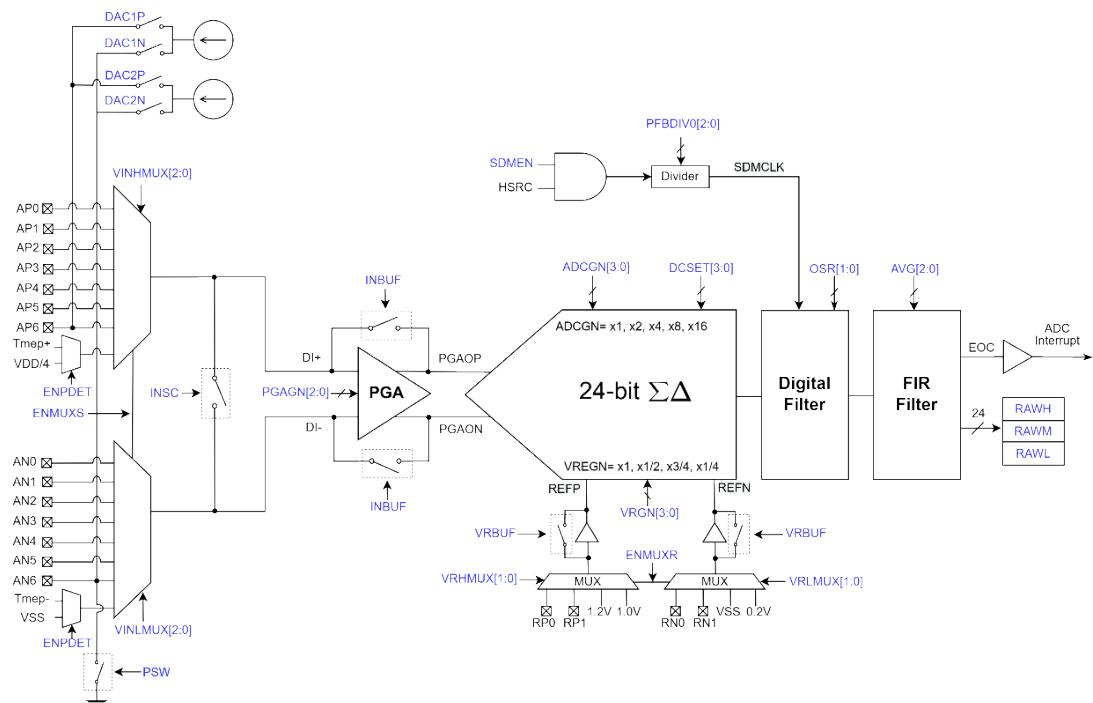

- Delta Sigma ADC (SDM)

- 1K samples per second

- 24-bit resolution

- External sensor calibration

- Temperature calibration

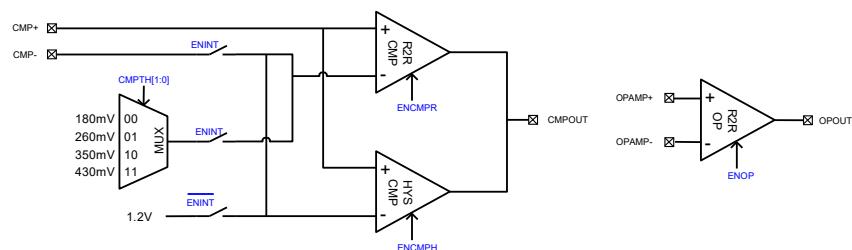

- Analog Controller (ANAC)

- Current source generation

- Comparator function

- Low voltage detection control

- Low voltage reset control

- Internal OPAMP

- General Purpose I/O (GPIO)

- 32 GPIOs, PA0 ~ PA7, PB0 ~ PB7, PC0 ~ PC7, PD0 ~ PD7

- Five GPIO modes

- ◆ Input mode

- ◆ Push-pull mode

- ◆ Open-drain mode

- ◆ Internal pull-up mode

- ◆ High-impedance mode

- PA2, PA3, PA5, PB3 can be configured as external interrupt sources with hardware debounce support

- Peripheral IOs are pin-shared with GPIOs

- Multi-Function ALU (MFA)

- 16-bit signed- or unsigned- multiplier

- IEEE754 floating point multiplier

- IEEE754 Log2 unit

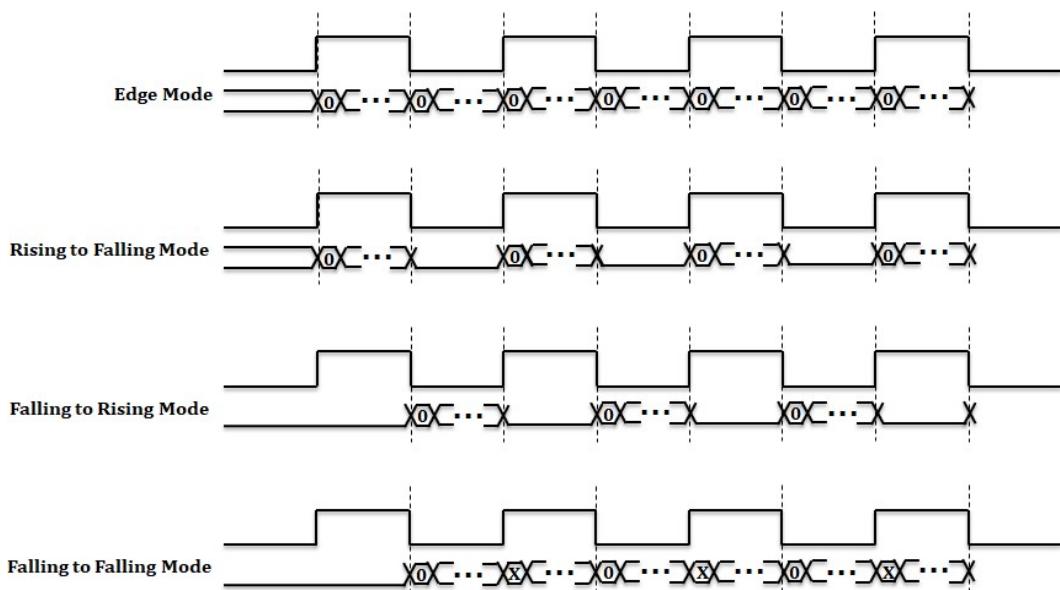

- Capture Controller (CAP)

- 4 channels for input capture function

- 4 capture modes

- ◆ Edge, rising to falling, falling to rising, falling to falling

- Capture input filter function

- Clocks

- Build-in 12MHz high speed RC oscillator

- Build-in 32KHz low speed RC oscillator

- External 12MHz or 32KHz crystal input

- Packages

- RoHS

- LQFP 48-pin

- QFN 48-pin

### 3 PARTS INFORMATION LIST

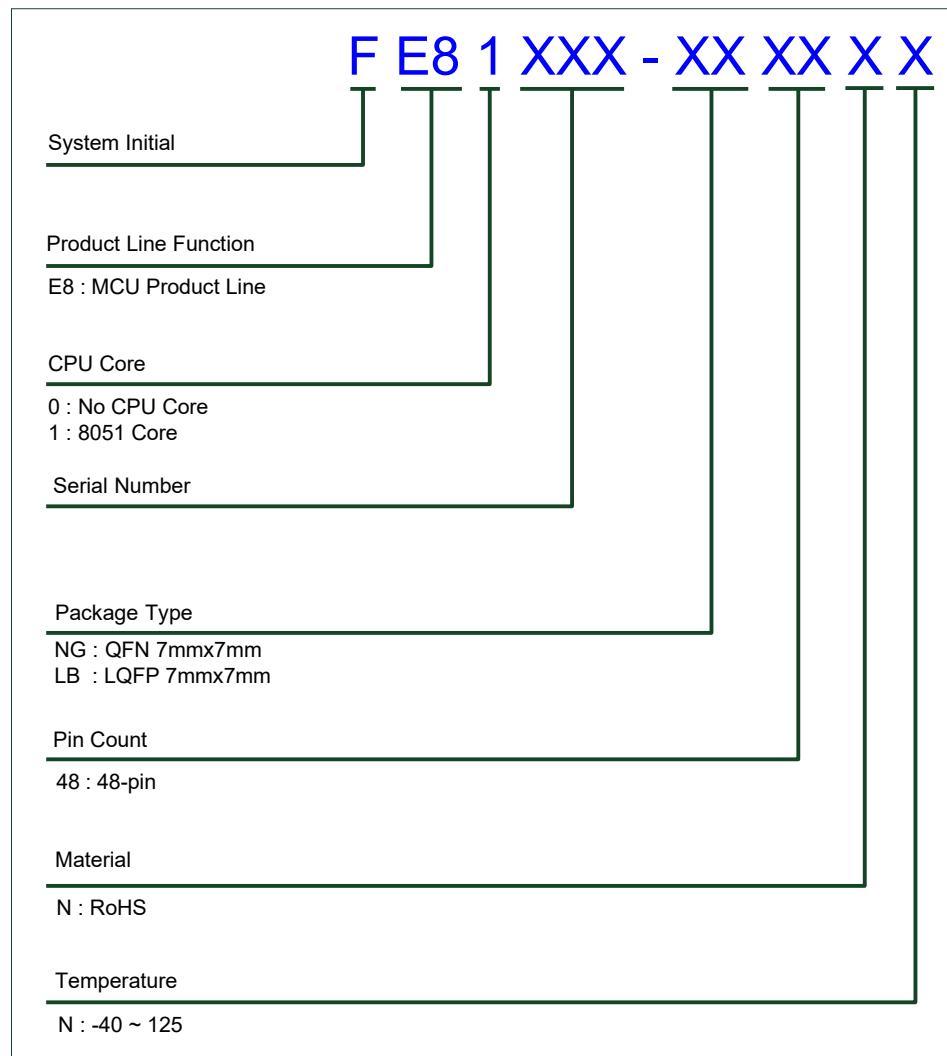

#### 3.1 ESMT FE81 Series Selection Guide

| Part No. | Flash | SRAM | IO | Timer PWM | UART | SPI | I2C | MFA | I2S | Comp. | ADC | ANAC | RTC | CAP | OCD ISP |

|----------|-------|------|----|-----------|------|-----|-----|-----|-----|-------|-----|------|-----|-----|---------|

| FE8116x  | 8KB   | 1KB  | 32 | 3         | 1    | 1   | 1   | 1   | —   | 1     | 1   | 1    | 1   | 1   | Y       |

Figure 3.1-1 FE81 Series Selection Code

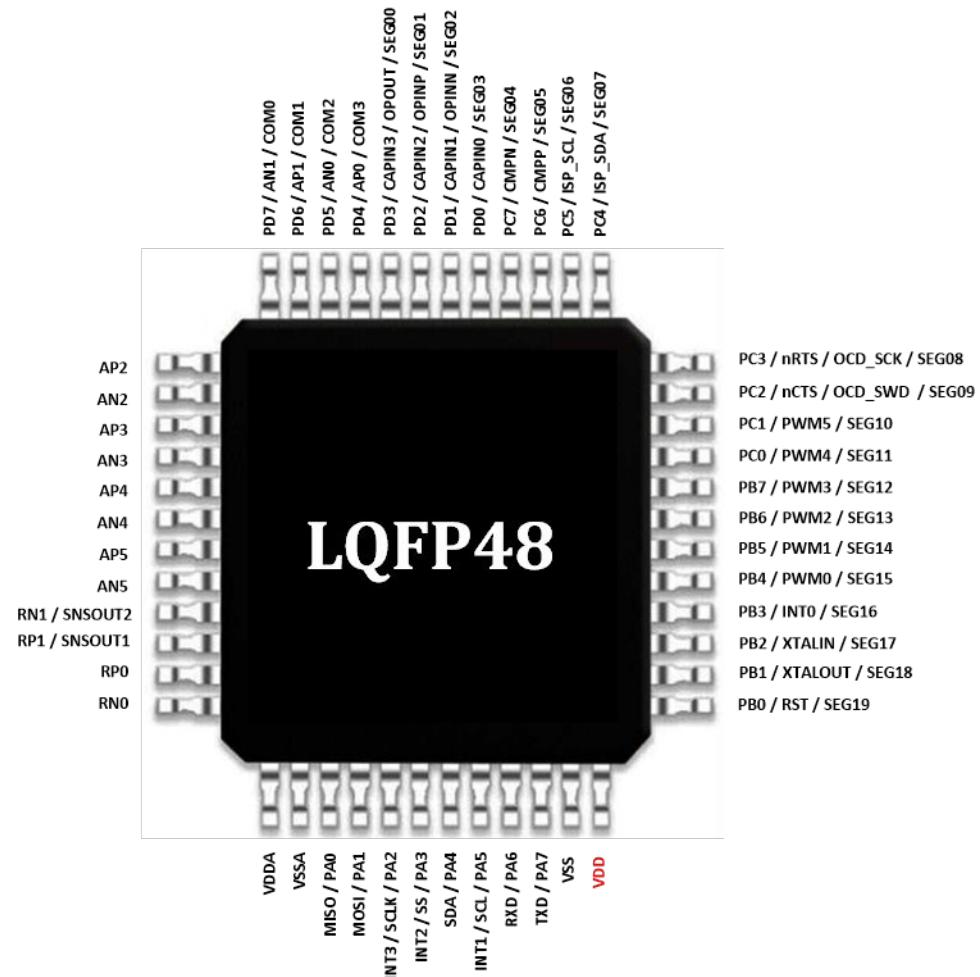

## 4 PIN CONFIGURATION

Figure 4-1 FE81 Series Pin Configuration

## 5 BLOCK DIAGRAM

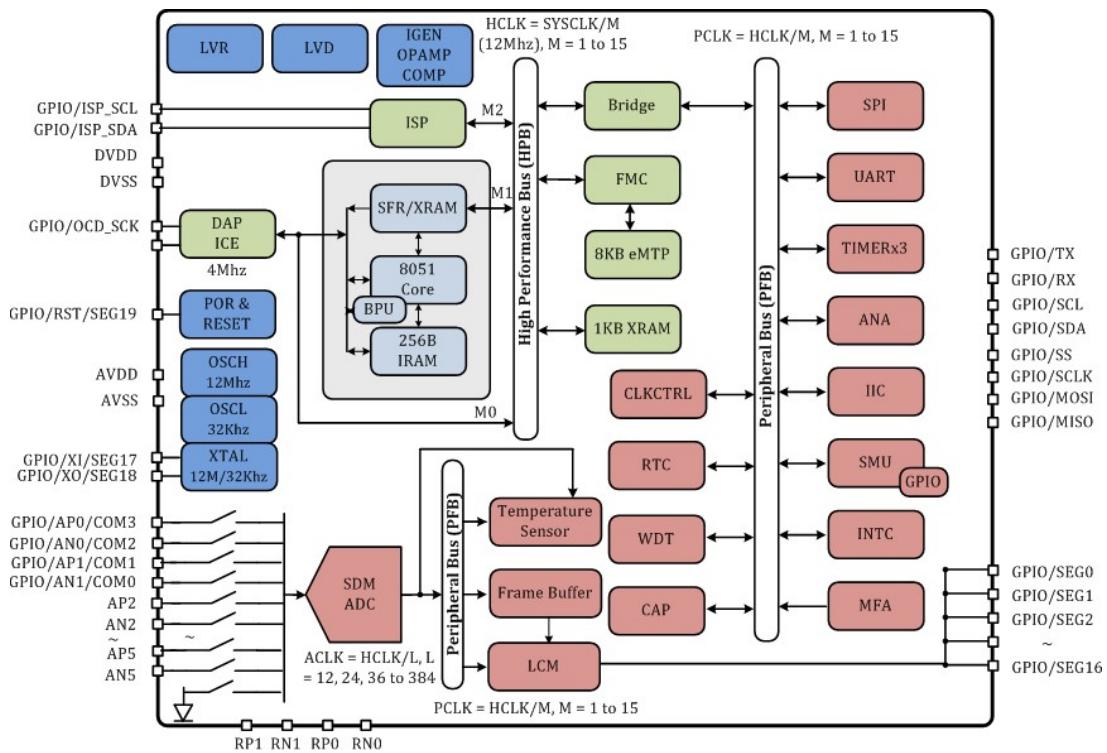

### 5.1 ESMT FE81 Series Block Diagram

Figure 5.1-1 FE81 Series Block Diagram

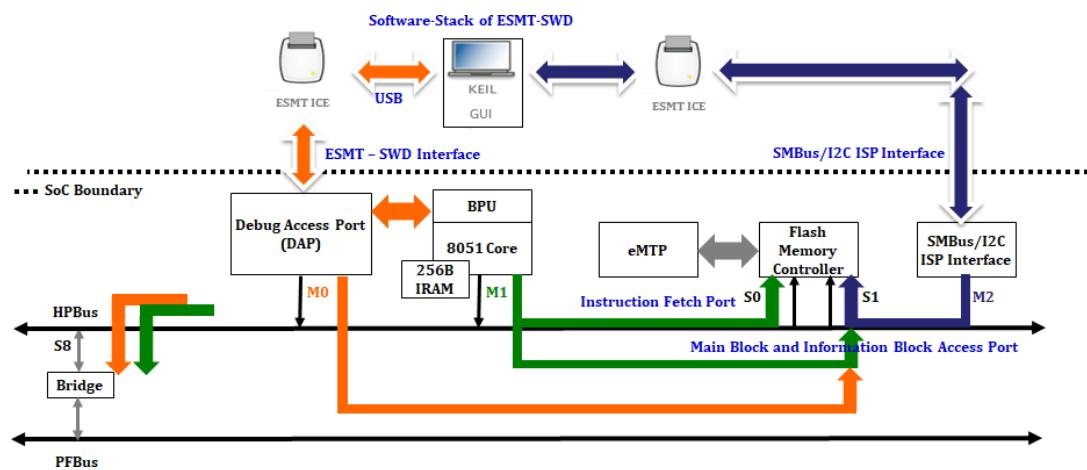

The block diagram of FE81 series is illustrated in Figure 5.1-1. The 1-T 8051 core, different from conventional 8051 architecture, accesses memory subsystem and peripherals via the same master port (M1), which increases the benefit of limitation of amount of peripherals and eases the system hardware cost as well. The 8051 core runs up to 12MHz with internal 256-byte I-RAM runs at the same frequency.

The Debug Access Port (DAP), cooperated with Break Point Unit (BPU), is responsible for 8051 core control, break points management and access of memory subsystem and all peripherals via master port (M0), which implements on-chip debugging function with commercial IDE tool. The DAP runs up to 4MHz based on the frequency of external 2-wire ESMT-SWD (OCD\_SCK, OCD\_SWD) interface.

The In System Programming (ISP), used to program on-chip flash memory via external “I2C protocol”, runs at the frequency of external I2C interface (Up to 400Kb/s) and achieves the purpose of application code on-line update.

The FE81 series supports eMTP flash memory instead of conventional flash memory which has the benefit of hardware cost, although the endurance cycle of eMTP is 1000 cycles. The eMTP has an information block region which can be used for user data storage, whereas the program code is stored at the main block region of the eMTP.

The Flash Memory Controller (FMC), used to access the eMTP, together with eMTP and 1K-byte X-RAM located at high performance bus (HPB) runs at the same frequency domain with the 8051 core.

The FE81 series supports rich peripherals that can be used for signal-conditioning, system peripherals and system connectivity. All these peripherals are located at the peripheral bus (PFB) with the frequency be able to be decreased at lower clock rate (Up to 12MHz). Below lists the peripheral functionalities.

| Functionality       | Peripheral                      |

|---------------------|---------------------------------|

| Signal Conditioning | Delta Sigma ADC                 |

|                     | External Sensor and Temperature |

| System Peripherals  | Real Time Clock                 |

|                     | Watchdog Timer                  |

|                     | Timer                           |

|                     | STN LCD Controller              |

|                     | Multi-function ALU              |

|                     | Analog Controller               |

|                     | Capture                         |

|                     | UART                            |

|                     | I2C                             |

| System Connectivity | SPI                             |

Table 5.1-1 Peripheral Functionality

The FE81 series supports 3 clock sources for general purpose applications, which are on-chip 12 MHz high speed RC oscillator, on-chip 32KHz low speed RC oscillator, and external 12MHz/32KHz crystal.

The other analog (ANAC) features include Low Voltage Detect (LVD), Low Voltage Reset (LVR), current source generation (I-GEN) for off-chip sensor application, internal comparator with external differential input, internal OPAMP with external differential input and output.

## 6 BLOCK FUNCTIONAL DESCRIPTION

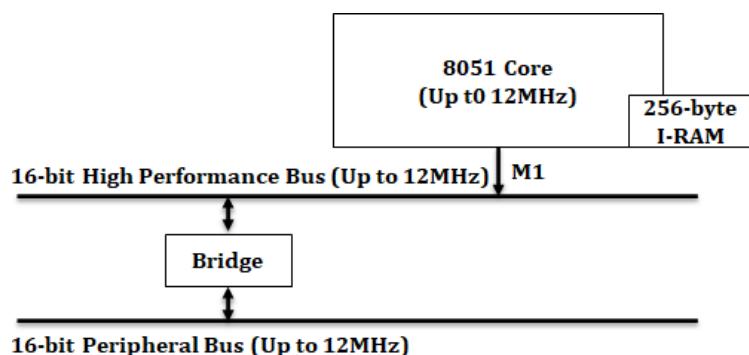

### 6.1 8051 Core and Bus Architecture

8051 is an 8-bit micro-controller designed for general purpose applications. Traditionally, 8051 uses three address buses to access memory subsystem and peripherals, where are I-RAM bus, SFR bus, and X-RAM bus. In ESMT FE81 series architecture, the I-RAM bus is used to access the internal 256-byte RAM as traditional 8051 does, however, the SFR bus and X-RAM bus are reduced to a single 16-bit high-performance bus and thus a larger memory addressing space is used for memory subsystem and peripherals without the limitation of the amounts of peripherals. That is, a more complicated bus matrix architecture is able to be used for more complicated MCU applications.

Figure 6.1-1 FE81 Series 8051 Core and Bus Architecture

Figure 6.1-1 depicts the 1T 8051 core and FE81 series bus architecture. This high-performance bus (HPB) runs at the same frequency with the 8051 core, and the frequency of the peripheral bus (PFB) can be decreased according to application requirements. For more detailed description, please refer to the clock architecture in section 6.5.

## 6.2 Memory Map Organization

### 6.2.1 FE81 Series Memory Map

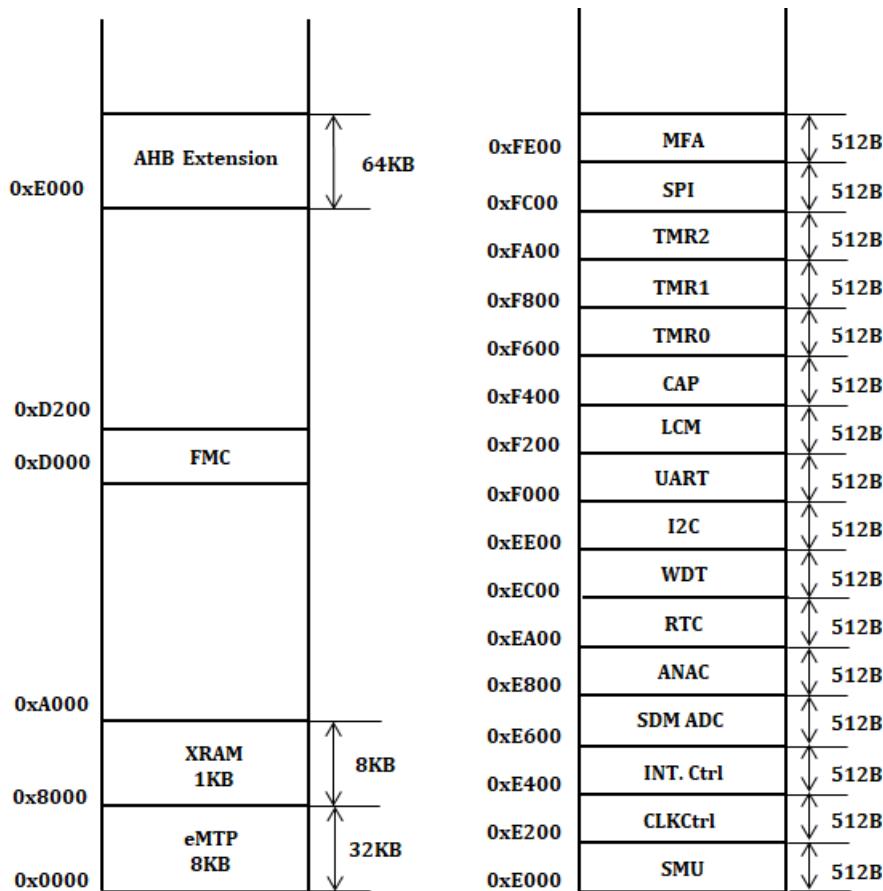

The FE81 series provides 64KB (16-bit) memory addressing space. The memory map of FE81 series is illustrated in Figure 6.2-1.

Figure 6.2-1 Memory Map of FE81 Series

The 0x0000 address is mapped to the 8K-byte eMTP for fetching application code by 8051 core after powering on. The 0x8000 address is mapped to the 1K-byte SRAM (X-RAM) for application data. The 0xD000 address is mapped to the flash memory controller (FMC) for accessing data from eMTP by 8051 core or DAP or ISP. The 0xE000 address is mapped to the peripherals for signal conditioning, system peripherals and system connectivity. Table 6.2-1 illustrates the detail information of FE81 series memory organization

| Address Space                                | Token      | Controllers                                         |

|----------------------------------------------|------------|-----------------------------------------------------|

| Flash and SRAMs Memory Space                 |            |                                                     |

| 0x0000 ~ 0x7FFF                              | FLASH_BA   | eMTP Flash Memory Space (32KB)<br>Only 8KB is used. |

| 0x8000 ~ 0xBFFF                              | XRAM_BA    | XRAM Memory Space (8KB)<br>Only 1KB is used.        |

| High Performance Bus (HPB) Controllers Space |            |                                                     |

| 0xD000 ~ 0xD1FF                              | FMC_BA     | FMC Memory Space (512B)                             |

| Peripheral Bus (PFB) Controllers Space       |            |                                                     |

| 0xE000 ~ 0xE1FF                              | SMU_BA     | System Management Unit Memory Space (512B)          |

| 0xE200 ~ 0xE3FF                              | CLKCTRL_BA | Clock Controller Memory Space (512B)                |

| 0xE400 ~ 0xE5FF                              | INTCTRL_BA | Interrupt Controller Memory Space (512B)            |

| 0xE600 ~ 0xE7FF                              | SDM_BA     | Delta Sigma ADC Memory Space (512B)                 |

| 0xE800 ~ 0xE9FF                              | ANAC_BA    | Analog Controller Memory Space (512B)               |

| 0xEA00 ~ 0xEBFF                              | RTC_BA     | Real-Time Clock Memory Space (512B)                 |

| 0xEC00 ~ 0xEDFF                              | WDT_BA     | Watchdog Memory Space (512B)                        |

| 0xEE00 ~ 0xEF00                              | I2C_BA     | I2C Memory Space (512B)                             |

| 0xF000 ~ 0xF1FF                              | UART_BA    | UART Memory Space (512B)                            |

| 0xF200 ~ 0xF3FF                              | LCM_BA     | LCD Controller Memory Space (512B)                  |

| 0xF400 ~ 0xF5FF                              | CAP_BA     | Capture Controller Memory Space (512B)              |

| 0xF600 ~ 0xF7FF                              | TMRO_BA    | Timer0 Memory Space (512B)                          |

| 0xF800 ~ 0xF9FF                              | TMR1_BA    | Timer1 Memory Space (512B)                          |

| 0xFA00 ~ 0xFBFF                              | TMR2_BA    | Timer2 Memory Space (512B)                          |

| 0xFC00 ~ 0xFDFF                              | SPI_BA     | SPI Memory Space (512B)                             |

| 0xFE00 ~ 0xFFFF                              | MFA_BA     | Multi-Function ALU Memory Space (512B)              |

Table 6.2-1 FE81 Series Memory Map Table

Table 6-2 illustrates all peripheral related register fields started from address 0xE000 to 0xFFFF. Please refer to each section of peripheral for detailed descriptions.

| Symbol                              | Description        | Offset | Bit Address & Symbol |         |         |         |         |         |         |         |         | Reset |

|-------------------------------------|--------------------|--------|----------------------|---------|---------|---------|---------|---------|---------|---------|---------|-------|

|                                     |                    |        | Bit7                 | Bit6    | Bit5    | Bit4    | Bit3    | Bit2    | Bit1    | Bit0    |         |       |

| Flash Memory Controller Base 0xD000 |                    |        |                      |         |         |         |         |         |         |         |         |       |

| FMCCON                              | FMC Control        | 0x00   | FMCEN                | INFOEN  | ISAVB   | —       | —       | —       | —       | —       | WDTOF   | 0x20  |

| FMCCMD                              | FMC Command        | 0x01   |                      |         |         |         | CMD     |         |         |         |         | 0x00  |

| FMCADRO                             | FMC Address0       | 0x02   |                      |         |         |         | FMADRO  |         |         |         |         | 0x00  |

| FMCADR1                             | FMC Address1       | 0x03   |                      |         |         |         | FMADR1  |         |         |         |         | 0x00  |

| FMCDATA0                            | FMC Data 0         | 0x04   |                      |         |         |         | FMDATO  |         |         |         |         | 0x00  |

| FMCDATA1                            | FMC Data 1         | 0x05   |                      |         |         |         | FMDAT1  |         |         |         |         | 0x00  |

| FMCSTAT                             | FMC Status         | 0x06   | BUSY                 | ECC     | —       | —       | —       | —       | —       | —       |         | 0x00  |

| FMCKSUM0                            | FMC Checksum 0     | 0x07   |                      |         |         |         | CKSUM0  |         |         |         |         | 0x00  |

| FMCKSUM1                            | FMC Checksum 1     | 0x08   |                      |         |         |         | CKSUM1  |         |         |         |         | 0x00  |

| System Management Unit Base 0xE000  |                    |        |                      |         |         |         |         |         |         |         |         |       |

| PNIDO                               | Part Number 0      | 0x00   |                      |         |         |         | PNIDO   |         |         |         |         | 0x00  |

| PNID1                               | Part Number 1      | 0x01   |                      |         |         |         | PNID1   |         |         |         |         | 0x00  |

| PNID2                               | Part Number 2      | 0x02   |                      |         |         |         | PNID2   |         |         |         |         | 0x00  |

| PNID3                               | Part Number 3      | 0x03   |                      |         |         |         | PNID3   |         |         |         |         | 0x00  |

| RSTSRC                              | Reset Source       | 0x04   | —                    | LVR     | —       | WDT     | CPU     | CHIP    | EXT     | POR     |         | 0x01  |

| SYRSRTC                             | System Reset       | 0x05   | —                    | —       | —       | —       | EXTR    | CPURH   | CPUR    | CHIPR   |         | 0x00  |

| PERRSTCO                            | Peripheral Reset 0 | 0x06   | UARTR                | I2CR    | —       | RTCR    | —       | LCMR    | ANAR    | SDMR    |         | 0x00  |

| PERRSTC1                            | Peripheral Reset 1 | 0x07   | —                    | —       | CAPR    | MFAR    | SPIR    | TMR2R   | TMR1R   | TMR0R   |         | 0x00  |

| PACTRLO                             | PA Control 0       | 0x08   | PA7CTL0              | PA6CTL0 | PA5CTL0 | PA4CTL0 | PA3CTL0 | PA2CTL0 | PA1CTL0 | PA0CTL0 |         | 0x0F  |

| PACTRL1                             | PA Control 1       | 0x09   | PA7CTL1              | PA6CTL1 | PA5CTL1 | PA4CTL1 | PA3CTL1 | PA2CTL1 | PA1CTL1 | PA0CTL1 |         | 0x0F  |

| PAMSO                               | PA Mode Select 0   | 0x0C   | PA7MOD0              | PA6MOD0 | PA5MOD0 | PA4MOD0 | PA3MOD0 | PA2MOD0 | PA1MOD0 | PA0MOD0 |         | 0x00  |

| PAMS1                               | PA Mode Select 1   | 0x0D   | PA7MOD1              | PA6MOD1 | PA5MOD1 | PA4MOD1 | PA3MOD1 | PA2MOD1 | PA1MOD1 | PA0MOD1 |         | 0x0F  |

| PAMS2                               | PA Mode Select 2   | 0x0E   | PA7MOD2              | PA6MOD2 | PA5MOD2 | PA4MOD2 | PA3MOD2 | PA2MOD2 | PA1MOD2 | PA0MOD2 |         | 0x00  |

| PADO0                               | PA0 DOUT           | 0x0F   | —                    | —       | —       | —       | —       | —       | —       | —       | PA0DOUT | 0x00  |

| PADO1                               | PA1 DOUT           | 0x10   | —                    | —       | —       | —       | —       | —       | —       | —       | PA1DOUT | 0x00  |

| PADO2                               | PA2 DOUT           | 0x11   | —                    | —       | —       | —       | —       | —       | —       | —       | PA2DOUT | 0x00  |

| PADO3                               | PA3 DOUT           | 0x12   | —                    | —       | —       | —       | —       | —       | —       | —       | PA3DOUT | 0x00  |

| PADO4                               | PA4 DOUT           | 0x13   | —                    | —       | —       | —       | —       | —       | —       | —       | PA4DOUT | 0x00  |

| PADO5                               | PA5 DOUT           | 0x14   | —                    | —       | —       | —       | —       | —       | —       | —       | PA5DOUT | 0x00  |

| PADO6                               | PA6 DOUT           | 0x15   | —                    | —       | —       | —       | —       | —       | —       | —       | PA6DOUT | 0x00  |

|                                  |                     |      |          |         |          |         |          |          |          |          |         |

|----------------------------------|---------------------|------|----------|---------|----------|---------|----------|----------|----------|----------|---------|

| PAD07                            | PA7 DOUT            | 0x16 | —        | —       | —        | —       | —        | —        | —        | PA7DOUT  | 0x00    |

| PAMSK                            | PA Mask             | 0x17 | PA7MSK   | PA6MSK  | PA5MSK   | PA4MSK  | PA3MSK   | PA2MSK   | PA1MSK   | PA0MSK   | 0x00    |

| PADOUT                           | PA DOUT             | 0x18 | PA7DOUT  | PA6DOUT | PA5DOUT  | PA4DOUT | PA3DOUT  | PA2DOUT  | PA1DOUT  | PA0DOUT  | 0x00    |

| PAPIN                            | PA Pin              | 0x19 | PA7      | PA6     | PA5      | PA4     | PA3      | PA2      | PA1      | PA0      | 0x00    |

| PBCTRL0                          | PB Control 0        | 0x1A | PB7CTL0  | PB6CTL0 | PB5CTL0  | PB4CTL0 | PB3CTL0  | PB2CTL0  | PB1CTL0  | PB0CTL0  | 0x07    |

| PBCTRL1                          | PB Control 1        | 0x1B | PB7CTL1  | PB6CTL1 | PB5CTL1  | PB4CTL1 | PB3CTL1  | PB2CTL1  | PB1CTL1  | PB0CTL1  | 0x00    |

| PBMS0                            | PB Mode Select 0    | 0x1E | PB7MOD0  | PB6MOD0 | PB5MOD0  | PB4MOD0 | PB3MOD0  | PB2MOD0  | PB1MOD0  | PB0MOD0  | 0x00    |

| PBMS1                            | PB Mode Select 1    | 0x1F | PB7MOD1  | PB6MOD1 | PB5MOD1  | PB4MOD1 | PB3MOD1  | PB2MOD1  | PB1MOD1  | PB0MOD1  | 0x00    |

| PBMS2                            | PB Mode Select 2    | 0x20 | PB7MOD2  | PB6MOD2 | PB5MOD2  | PB4MOD2 | PB3MOD2  | PB2MOD2  | PB1MOD2  | PB0MOD2  | 0x00    |

| PBDO0                            | PB0 DOUT            | 0x21 | —        | —       | —        | —       | —        | —        | —        | PB0DOUT  | 0x00    |

| PBDO1                            | PB1 DOUT            | 0x22 | —        | —       | —        | —       | —        | —        | —        | PB1DOUT  | 0x00    |

| PBDO2                            | PB2 DOUT            | 0x23 | —        | —       | —        | —       | —        | —        | —        | PB2DOUT  | 0x00    |

| PBDO3                            | PB3 DOUT            | 0x24 | —        | —       | —        | —       | —        | —        | —        | PB3DOUT  | 0x00    |

| PBDO4                            | PB4 DOUT            | 0x25 | —        | —       | —        | —       | —        | —        | —        | PB4DOUT  | 0x00    |

| PBDO5                            | PB5 DOUT            | 0x26 | —        | —       | —        | —       | —        | —        | —        | PB5DOUT  | 0x00    |

| PBDO6                            | PB6 DOUT            | 0x27 | —        | —       | —        | —       | —        | —        | —        | PB6DOUT  | 0x00    |

| PBDO7                            | PB7 DOUT            | 0x28 | —        | —       | —        | —       | —        | —        | —        | PB7DOUT  | 0x00    |

| PBMSK                            | PB Mask             | 0x29 | PB7MSK   | PB6MSK  | PB5MSK   | PB4MSK  | PB3MSK   | PB2MSK   | PB1MSK   | PB0MSK   | 0x00    |

| PBDOUT                           | PB DOUT             | 0x2A | PB7DOUT  | PB6DOUT | PB5DOUT  | PB4DOUT | PB3DOUT  | PB2DOUT  | PB1DOUT  | PB0DOUT  | 0x00    |

| PBPIN                            | PB Pin              | 0x2B | PB7      | PB6     | PB5      | PB4     | PB3      | PB2      | PB1      | PB0      | 0x00    |

| PCCTRL0                          | PC Control 0        | 0x2C | PC7CTL0  | PC6CTL0 | PC5CTL0  | PC4CTL0 | PC3CTL0  | PC2CTL0  | PC1CTL0  | PC0CTL0  | 0x00    |

| PCCTRL1                          | PC Control 1        | 0x2D | PC7CTL1  | PC6CTL1 | PC5CTL1  | PC4CTL1 | PC3CTL1  | PC2CTL1  | PC1CTL1  | PC0CTL1  | 0x00    |

| PCMS0                            | PC Mode Select 0    | 0x30 | PC7MOD0  | PC6MOD0 | PC5MOD0  | PC4MOD0 | PC3MOD0  | PC2MOD0  | PC1MOD0  | PC0MOD0  | 0x00    |

| PCMS1                            | PC Mode Select 1    | 0x31 | PC7MOD1  | PC6MOD1 | PC5MOD1  | PC4MOD1 | PC3MOD1  | PC2MOD1  | PC1MOD1  | PC0MOD1  | 0x00    |

| PCMS2                            | PC Mode Select 2    | 0x32 | PC7MOD2  | PC6MOD2 | PC5MOD2  | PC4MOD2 | PC3MOD2  | PC2MOD2  | PC1MOD2  | PC0MOD2  | 0x00    |

| PCD00                            | PC0 DOUT            | 0x33 | —        | —       | —        | —       | —        | —        | —        | PC0DOUT  | 0x00    |

| PCD01                            | PC1 DOUT            | 0x34 | —        | —       | —        | —       | —        | —        | —        | PC1DOUT  | 0x00    |

| PCD02                            | PC2 DOUT            | 0x35 | —        | —       | —        | —       | —        | —        | —        | PC2DOUT  | 0x00    |

| PCD03                            | PC3 DOUT            | 0x36 | —        | —       | —        | —       | —        | —        | —        | PC3DOUT  | 0x00    |

| PCD04                            | PC4 DOUT            | 0x37 | —        | —       | —        | —       | —        | —        | —        | PC4DOUT  | 0x00    |

| PCD05                            | PC5 DOUT            | 0x38 | —        | —       | —        | —       | —        | —        | —        | PC5DOUT  | 0x00    |

| PCD06                            | PC6 DOUT            | 0x39 | —        | —       | —        | —       | —        | —        | —        | PC6DOUT  | 0x00    |

| PCD07                            | PC7 DOUT            | 0x3A | —        | —       | —        | —       | —        | —        | —        | PC7DOUT  | 0x00    |

| PCMSK                            | PC Mask             | 0x3B | PC7MSK   | PC6MSK  | PC5MSK   | PC4MSK  | PC3MSK   | PC2MSK   | PC1MSK   | PC0MSK   | 0x00    |

| PCDOUT                           | PC DOUT             | 0x3C | PC7DOUT  | PC6DOUT | PC5DOUT  | PC4DOUT | PC3DOUT  | PC2DOUT  | PC1DOUT  | PC0DOUT  | 0x00    |

| PCPIN                            | PC Pin              | 0x3D | PC7      | PC6     | PC5      | PC4     | PC3      | PC2      | PC1      | PC0      | 0x00    |

| PDCTRL0                          | PD Control 0        | 0x3E | PD7CTL0  | PD6CTL0 | PD5CTL0  | PD4CTL0 | PD3CTL0  | PD2CTL0  | PD1CTL0  | PD0CTL0  | 0x00    |

| PDCTRL1                          | PD Control 1        | 0x3F | PD7CTL1  | PD6CTL1 | PD5CTL1  | PD4CTL1 | PD3CTL1  | PD2CTL1  | PD1CTL1  | PD0CTL1  | 0x00    |

| PDMS0                            | PD Mode Select 0    | 0x42 | PD7MOD0  | PD6MOD0 | PD5MOD0  | PD4MOD0 | PD3MOD0  | PD2MOD0  | PD1MOD0  | PD0MOD0  | 0x00    |

| PDMS1                            | PD Mode Select 1    | 0x43 | PD7MOD1  | PD6MOD1 | PD5MOD1  | PD4MOD1 | PD3MOD1  | PD2MOD1  | PD1MOD1  | PD0MOD1  | 0x00    |

| PDMS2                            | PD Mode Select 2    | 0x44 | PD7MOD2  | PD6MOD2 | PD5MOD2  | PD4MOD2 | PD3MOD2  | PD2MOD2  | PD1MOD2  | PD0MOD2  | 0x00    |

| PDD00                            | PD0 DOUT            | 0x45 | —        | —       | —        | —       | —        | —        | —        | PDD0DOUT | 0x00    |

| PDD01                            | PD1 DOUT            | 0x46 | —        | —       | —        | —       | —        | —        | —        | PDD1DOUT | 0x00    |

| PDD02                            | PD2 DOUT            | 0x47 | —        | —       | —        | —       | —        | —        | —        | PDD2DOUT | 0x00    |

| PDD03                            | PD3 DOUT            | 0x48 | —        | —       | —        | —       | —        | —        | —        | PDD3DOUT | 0x00    |

| PDD04                            | PD4 DOUT            | 0x49 | —        | —       | —        | —       | —        | —        | —        | PDD4DOUT | 0x00    |

| PDD05                            | PD5 DOUT            | 0x4A | —        | —       | —        | —       | —        | —        | —        | PDD5DOUT | 0x00    |

| PDD06                            | PD6 DOUT            | 0x4B | —        | —       | —        | —       | —        | —        | —        | PDD6DOUT | 0x00    |

| PDD07                            | PD7 DOUT            | 0x4C | —        | —       | —        | —       | —        | —        | —        | PDD7DOUT | 0x00    |

| PDMSK                            | PD Mask             | 0x4D | PD7MSK   | PD6MSK  | PD5MSK   | PD4MSK  | PD3MSK   | PD2MSK   | PD1MSK   | PD0MSK   | 0x00    |

| PDDOUT                           | PD DOUT             | 0x4E | PD7DOUT  | PD6DOUT | PD5DOUT  | PD4DOUT | PD3DOUT  | PD2DOUT  | PD1DOUT  | PD0DOUT  | 0x00    |

| PDPIN                            | PD Pin              | 0x4F | PD7      | PD6     | PD5      | PD4     | PD3      | PD2      | PD1      | PDO      | 0x00    |

| TMRSTAL                          | Timer Stall         | 0x50 | —        | —       | —        | —       | —        | —        | TMR2ST   | TMR1ST   | TMR0ST  |

| RAMCONF                          | RAM Config.         | 0x51 | MS       |         |          |         | MSE      |          |          |          | DVS     |

| Clock Controller Base 0xE200     |                     |      |          |         |          |         |          |          |          |          |         |

| CLKEN                            | CK Enable           | 0x00 | —        | —       | —        | XTALSEL | —        | —        | LSRCEN   | HSRCEN   | XTALEN  |

| CLKSTB                           | CK Stable           | 0x01 | —        | —       | —        | —       | —        | —        | LSRCSTB  | HSRCSTB  | XTALSTB |

| CLKSEL                           | CK Selection        | 0x02 | TMR2SRC  | TMR1SRC | TMROSRC  | EINTSRC | RTCSRC   | PMUSRC   | SYSSRC   |          |         |

| HPBCLKC                          | HP. Bus CK Contr.   | 0x03 | —        | —       | —        | —       | FMCEN    | PFBEN    | HPBEN    | MCUEN    | 0x07    |

| PFBCLKC0                         | PF. Bus CK Contr. 0 | 0x04 | UARTEN   | I2CEN   | WDTEN    | RTCEN   | —        | LCMEN    | ANAEEN   | SDMEN    | 0x00    |

| PFBCLKC1                         | PF. Bus CK Contr. 1 | 0x05 | PDEN     | PCEN    | PBEN     | PAEN    | SPIEN    | TMR2EN   | TMR1EN   | TMR0EN   | 0x00    |

| PFBCLKC2                         | PF. Bus CK Contr. 2 | 0x06 | —        | —       | —        | —       | CAPEN    | MFAEN    | EINTEN   | 0x00     |         |

| SYSDIV                           | System CK Div.      | 0x07 | PFB_N    |         |          |         | MCU_N    |          |          |          | 0x00    |

| PFBDIV0                          | PF. Bus CK Div. 0   | 0x08 | TMR0_N   |         | —        | —       | —        | SDM_N    |          |          |         |

| PFBDIV1                          | PF. Bus CK Div. 1   | 0x09 | —        | —       | —        | —       | TMR2_N   | —        | TMR1_N   | —        | 0x00    |

| PMCON                            | Power Mode          | 0x0A | —        | —       | —        | —       | —        | —        | —        | PMCON    | 0x00    |

| CLKTRIM                          | CK Trim             | 0x10 | HSRCH    |         | HSRCL    |         |          |          |          |          | 0x00    |

| Interrupt Controller Base 0xE400 |                     |      |          |         |          |         |          |          |          |          |         |

| GINTMSK                          | Global INT. Mask    | 0x00 | —        | —       | —        | —       | —        | —        | —        | GINTEN   | 0x00    |

| EINTCTRL                         | EINT. Control       | 0x01 | EINT3CTL |         | EINT2CTL |         | EINT1CTL |          | EINTOCTL |          |         |

| EINTEN                           | EINT. Enable        | 0x02 | —        | —       | —        | —       | EINT3EN  | EINT2EN  | EINT1EN  | EINTOEN  | 0x00    |

| DBCTRL                           | EINT Deb. Control   | 0x03 | —        | —       | —        | —       | DBSAM/PC |          |          |          |         |

| EINTSTAT                         | EINT Status         | 0x04 | —        | —       | —        | —       | EINT3F   | EINT2F   | EINT1F   | EINTOF   | 0x00    |

| INTSTAT0                         | Peri. INT. STAT 0   | 0x05 | WDTINTF  | RTCINTF | SDMINTF  | —       | EINT3F   | EINT2F   | EINT1F   | EINTOF   | 0x00    |

| INTSTAT1                         | Peri. INT. STAT 1   | 0x06 | —        | SPINTF  | UARTINTF | I2CINTF | —        | TMR2INTF | TMR1INTF | TMR0INTF | 0x00    |

| IRQNUM                           | IRQ Number          | 0x07 | —        | —       | —        | —       | IRQNUM   |          |          |          |         |

| IRQCLR                           | IRQ Clear           | 0x08 | —        | —       | —        | —       | —        | —        | —        | IRQCLR   | 0x00    |

| Delta Sigma ADC Base 0xE600      |                     |      |          |         |          |         |          |          |          |          |         |

| RAWL                             | Raw Data L          | 0x00 | RAWL     |         |          |         |          |          |          |          |         |

| RAWM                             | Raw Data M          | 0x01 | RAWM     |         |          |         |          |          |          |          |         |

| RAWH                             | Raw Data H          | 0x02 | RAWH     |         |          |         |          |          |          |          |         |

| CLBL                             | Calibration Data L  | 0x03 | CLBL     |         |          |         |          |          |          |          |         |

| CLBM                             | Calibration Data M  | 0x04 | CLBM     |         |          |         |          |          |          |          |         |

| CLBH                             | Calibration Data H  | 0x05 | CLBH     |         |          |         |          |          |          |          |         |

| SDMGAINL                         | Sensor Clb. Gain L  | 0x06 | SDMGAINL |         |          |         |          |          |          |          |         |

| SDMGAINM                         | Sensor Clb. Gain M  | 0x07 | SDMGAINM |         |          |         |          |          |          |          |         |

| SDMGAINH                         | Sensor Clb. Gain H  | 0x08 | SDMGAINH |         |          |         |          |          |          |          |         |

|                               |                     |      |             |         |         |         |            |          |          |          |          |         |      |      |  |      |  |  |  |  |

|-------------------------------|---------------------|------|-------------|---------|---------|---------|------------|----------|----------|----------|----------|---------|------|------|--|------|--|--|--|--|

| SDMOSL                        | Sensor Clb. OS L    | 0x09 | S_CLB_OSL   |         |         |         |            |          |          |          |          |         | 0x00 |      |  |      |  |  |  |  |

| SDMOSM                        | Sensor Clb. OS M    | 0x0A | S_CLB_OSM   |         |         |         |            |          |          |          |          |         | 0x00 |      |  |      |  |  |  |  |

| SDMOSH                        | Sensor Clb. OS H    | 0x0B | S_CLB_OSH   |         |         |         |            |          |          |          |          |         | 0x00 |      |  |      |  |  |  |  |

| SDMOFL                        | Sensor Clb. OF L    | 0x0C | S_CLB_OFL   |         |         |         |            |          |          |          |          |         | 0x00 |      |  |      |  |  |  |  |

| SDMOFM                        | Sensor Clb. OF M    | 0x0D | S_CLB_OFM   |         |         |         |            |          |          |          |          |         | 0x00 |      |  |      |  |  |  |  |

| SDMOFH                        | Sensor Clb. OF H    | 0x0E | S_CLB_OFH   |         |         |         |            |          |          |          |          |         | 0x00 |      |  |      |  |  |  |  |

| TEMPGAINL                     | Temp. Clb. Gain L   | 0x0F | T_CLB_GAINL |         |         |         |            |          |          |          |          |         | 0x00 |      |  |      |  |  |  |  |

| TEMPGAINM                     | Temp. Clb. Gain M   | 0x10 | T_CLB_GAINM |         |         |         |            |          |          |          |          |         | 0x00 |      |  |      |  |  |  |  |

| TEMPGAINH                     | Temp. Clb. Gain H   | 0x11 | T_CLB_GAINH |         |         |         |            |          |          |          |          |         | 0x00 |      |  |      |  |  |  |  |

| TEMPPOS                       | Temp. Clb. OS L     | 0x12 | T_CLB_OSL   |         |         |         |            |          |          |          |          |         | 0x00 |      |  |      |  |  |  |  |

| TEMPOSM                       | Temp. Clb. OS M     | 0x13 | T_CLB_OSM   |         |         |         |            |          |          |          |          |         | 0x00 |      |  |      |  |  |  |  |

| TEMPOSH                       | Temp. Clb. OS H     | 0x14 | T_CLB_OSH   |         |         |         |            |          |          |          |          |         | 0x00 |      |  |      |  |  |  |  |

| TEMPOFL                       | Temp. Clb. OF L     | 0x15 | T_CLB_OFL   |         |         |         |            |          |          |          |          |         | 0x00 |      |  |      |  |  |  |  |

| TEMPOFM                       | Temp. Clb. OF M     | 0x16 | T_CLB_OFM   |         |         |         |            |          |          |          |          |         | 0x00 |      |  |      |  |  |  |  |

| TEMPOFH                       | Temp. Clb. OF H     | 0x17 | T_CLB_OFH   |         |         |         |            |          |          |          |          |         | 0x00 |      |  |      |  |  |  |  |

| OSR                           | Over-Sampling       | 0x18 | —           | —       | —       | —       | OSR        |          |          |          | 0x00     |         |      |      |  |      |  |  |  |  |

| INMUX                         | Input Mux           | 0x19 | ENMUXS      | —       | VINLMUX |         |            |          | VINHMUX  |          |          |         | 0x00 |      |  |      |  |  |  |  |

| RMUX                          | Refer. Mux          | 0x1A | ENMUXR      | —       | —       | —       | VRLMUX     |          |          |          | VRHMUX   |         |      | 0x00 |  |      |  |  |  |  |

| PGASET                        | Enable Set          | 0x1B | ENBUFCFH    | VRBUF   | ENPGACH | INBUF   | —          | —        | PGAGN    |          |          |         | 0x00 |      |  |      |  |  |  |  |

| ENCFG                         | Config              | 0x1C | ENADC       | ENADCCH | VRGN    |         |            |          | ADCGN    |          |          |         | 0x00 |      |  |      |  |  |  |  |

| DCSET                         | DC Set              | 0x1D | —           | —       | —       | —       | —          | —        | DCSET    |          |          |         | 0x00 |      |  |      |  |  |  |  |

| CONFIG                        | Config. Set         | 0x1E | —           | —       | FCHSEL  | FTCHK   | —          | —        | ENDEM    | ENNSNSCH | ENTMPSNS | 0x00    |      |      |  |      |  |  |  |  |

| INTSTAT                       | INT. Status         | 0x1F | INTF        | —       | —       | —       | —          | —        | —        | —        | INTEN    | 0x00    |      |      |  |      |  |  |  |  |

| TEST                          | Test Set            | 0x80 | —           | —       | —       | —       | CALDVDC    | INCH1    | INCH0    | INSC     | 0x00     |         |      |      |  |      |  |  |  |  |

| Analog Controller Base 0xE800 |                     |      |             |         |         |         |            |          |          |          |          |         |      |      |  |      |  |  |  |  |

| COMPFCFG                      | Comp. Config.       | 0x00 | CMPPHYS     |         |         |         | CMPTH      |          | CMPIVTH  | CMPPHEN  | CMPPREN  | 0x00    |      |      |  |      |  |  |  |  |

| COMPRES                       | Comp. Result        | 0x01 | —           | —       | —       | —       | —          | —        | —        | —        | CMPOUT   | 0x00    |      |      |  |      |  |  |  |  |

| LVCFCFG                       | Low Volt. Config.   | 0x02 | LVDF        | LVDLV   |         |         |            | LVRLV    |          | LVDEN    | LVREN    | 0x00    |      |      |  |      |  |  |  |  |

| LVDIEN                        | LVD Interrupt En.   | 0x03 | —           | —       | —       | —       | —          | —        | —        | —        | LVDIEN   | 0x00    |      |      |  |      |  |  |  |  |

| PWCFG                         | Power Config.       | 0x04 | —           | ENOPAMP | ENBODN  | ENBODP  | ENPDDET    | ENVCM    | ENLDOA   | ENBIAS   | 0x00     |         |      |      |  |      |  |  |  |  |

| IGENCTRL                      | Cur. Gen. Contr.    | 0x05 | —           | PSW     |         |         |            | DAC2N    | DAC1N    | DAC2P    | DAC1P    | 0x00    |      |      |  |      |  |  |  |  |

| IGEN1                         | Cur. Gen. En1.      | 0x06 | ENIDAC1     | IDAC1   |         |         |            |          |          |          |          |         |      | 0x00 |  |      |  |  |  |  |

| IGEN2                         | Cur. Gen. En2       | 0x07 | ENIDAC2     | IDAC2   |         |         |            |          |          |          |          |         |      | 0x00 |  |      |  |  |  |  |

| IGENTRIM1                     | Cur. Gen. Trim 1    | 0x08 | IDAC1TR     |         |         |         |            |          |          |          |          |         | 0x00 |      |  |      |  |  |  |  |

| IGENTRIM2                     | Cur. Gen. Trim 2    | 0x09 | IDAC2TR     |         |         |         |            |          |          |          |          |         | 0x00 |      |  |      |  |  |  |  |

| BGTRIM                        | BG Trim             | 0x0A | ENBGTR      | —       | —       | BG_TRIM |            |          |          |          |          |         |      |      |  | 0x00 |  |  |  |  |

| Real-Time Clock Base 0xEAO0   |                     |      |             |         |         |         |            |          |          |          |          |         |      | 0x00 |  |      |  |  |  |  |

| CNTSEC                        | Second Counter      | 0x00 | —           | —       | CNTSEC  |         |            |          | CNTMIN   |          |          |         | 0x00 |      |  |      |  |  |  |  |

| CNTMIN                        | Minute Counter      | 0x01 | —           | —       | CNTMIN  |         |            |          | CNTHOUR  |          |          |         | 0x00 |      |  |      |  |  |  |  |

| CNTHOUR                       | Hour Counter        | 0x02 | —           | —       | —       | CNTHOUR |            |          |          | CNTDAY   |          |         |      | 0x00 |  |      |  |  |  |  |

| CNTDAY                        | Day Counter         | 0x03 | —           | —       | —       | CNTDAY  |            |          |          | ALMSEC   |          |         |      | 0x00 |  |      |  |  |  |  |

| ALMSEC                        | Second Alarm        | 0x04 | —           | —       | ALMSEC  |         |            |          | ALMMIN   |          |          |         | 0x00 |      |  |      |  |  |  |  |

| ALMMIN                        | Minute Alarm        | 0x05 | —           | —       | ALMMIN  |         |            |          | ALMHOUR  |          |          |         | 0x00 |      |  |      |  |  |  |  |

| ALMHOUR                       | Hour Alarm          | 0x06 | —           | —       | —       | ALMHOUR |            |          |          | RTCEN    |          |         |      | 0x00 |  |      |  |  |  |  |

| RTCCTRL                       | RTC Control         | 0x07 | —           | SEC1EN  | MIN1EN  | HOR1EN  | DAY1EN     | ALM1EN   | ALMWEN   | RTCTEN   | 0x00     |         |      |      |  |      |  |  |  |  |

| RTCSTAT                       | RTC Status          | 0x08 | —           | SEC1NTF | MIN1NTF | HOR1NTF | DAY1NTF    | ALM1NTF  | 0x00     |          |          |         | 0x00 |      |  |      |  |  |  |  |

| RTCWDONE                      | RTC Write Done      | 0x09 | —           | —       | —       | —       | —          | —        | —        | —        | WDONE    | 0x00    |      |      |  |      |  |  |  |  |

| Watchdog Base 0xEC00          |                     |      |             |         |         |         |            |          |          |          |          |         |      | 0x00 |  |      |  |  |  |  |

| WDTCTRL0                      | WDT Control 0       | 0x00 | —           | RSTTIME |         |         |            | —        | INTTIME  |          |          |         | 0x00 |      |  |      |  |  |  |  |

| WDTCTRL1                      | WDT Control 1       | 0x01 | —           | —       | —       | —       | RSTEN      | INTEN    | CLKSEL   | WDTEN    | 0x00     |         |      |      |  |      |  |  |  |  |

| RESTART                       | Restart             | 0x02 | 0x5A        |         |         |         |            |          |          |          |          |         | 0x5A |      |  |      |  |  |  |  |

| WRPROT                        | Write Protect       | 0x03 | 0xA5        |         |         |         |            |          |          |          |          |         | 0xA5 |      |  |      |  |  |  |  |

| STATUS                        | Status              | 0x04 | —           | —       | —       | —       | —          | —        | —        | —        | —        | WDTINTF | 0x00 |      |  |      |  |  |  |  |

| I2C Base 0xEE00               |                     |      |             |         |         |         |            |          |          |          |          |         |      | 0x00 |  |      |  |  |  |  |

| HWCFG                         | HW FIFO Config.     | 0x00 | —           | —       | —       | —       | —          | —        | FIFOSIZE |          |          |         | 0x00 |      |  |      |  |  |  |  |

| OSCRCTRL                      | Over-Samp. Rate     | 0x01 | —           | —       | —       | —       | OSCR       |          |          |          | 0x00     |         |      |      |  |      |  |  |  |  |

| DATA_DLL                      | Receive Buffer      | 0x02 | RBR         |         |         |         |            |          |          |          |          |         | 0x00 |      |  |      |  |  |  |  |

|                               | Transmitter Holding |      | THR         |         |         |         |            |          |          |          |          |         |      |      |  |      |  |  |  |  |

|                               | Div. LSB            |      | DLL         |         |         |         |            |          |          |          |          |         |      |      |  |      |  |  |  |  |

| IER_DLM                       | Interrupt Enable    | 0x03 | —           | —       | —       | —       | EMS1       | ELSI     | ETHE1    | ERBI     | 0x00     |         |      |      |  |      |  |  |  |  |

|                               | Div. MSB            |      | DLM         |         |         |         |            |          |          |          |          |         | 0x00 |      |  |      |  |  |  |  |

| IIR_FCR                       | Interrupt Iden.     | 0x04 | FIFOED      | FIFOED  | —       | —       | INTRID     |          |          |          | 0x00     |         |      |      |  |      |  |  |  |  |

|                               | FIFO Control        |      | RFIFOT      | RFIFOT  | TFIFOT  | TFIFOT  | —          | TFIFORST | RFIFORST | FIFOE    | 0x00     |         |      |      |  |      |  |  |  |  |

| LINECTRL                      | Line Control        | 0x05 | DLAB        | BC      | SPS     | EPS     | PEN        | STB      | WLS      |          |          |         | 0x00 |      |  |      |  |  |  |  |

| MODMCFG                       | Modem Control       | 0x06 | —           | —       | AFCE    | LOOP    | —          | —        | RTS      | —        | —        | DR      | 0x00 |      |  |      |  |  |  |  |

| LINESTAT                      | Line Status         | 0x07 | ERRF        | TEMF    | THEF    | LBREAK  | FERR       | PERR     | OERR     | DR       | 0x00     |         |      |      |  |      |  |  |  |  |

| MODMSTAT                      | Modem Status        | 0x08 | —           | —       | —       | CTS     | —          | —        | —        | DCTS     | 0x00     |         |      |      |  |      |  |  |  |  |

| LCD Controller Base 0xF200    |                     |      |             |         |         |         |            |          |          |          |          |         |      | 0x00 |  |      |  |  |  |  |

| LCMCTRL0                      | LCM Control 0       | 0x00 | —           | ENBUF   | FREQ    | LEVEL   | VCTR       |          |          |          | 0x00     |         |      |      |  |      |  |  |  |  |

| LCMCTRL1                      | LCM Control 1       | 0x01 | —           | —       | —       | —       | —          | —        | —        | —        | LCMEN    | 0x00    |      |      |  |      |  |  |  |  |

| SEQBUFO0                      | Frame Buffer 00     | 0x10 | —           | —       | —       | —       | FRAMEBUFO0 |          |          |          | 0x00     |         |      |      |  |      |  |  |  |  |

|                                                                 |                    |      |                |          |             |          |                |           |  |  |  |

|-----------------------------------------------------------------|--------------------|------|----------------|----------|-------------|----------|----------------|-----------|--|--|--|

| SEQBUFO1                                                        | Frame Buffer 01    | 0x11 | —              | —        | —           | —        | FRAMEBUFO1     | 0x00      |  |  |  |

| SEQBUFO2                                                        | Frame Buffer 02    | 0x12 | —              | —        | —           | —        | FRAMEBUFO2     | 0x00      |  |  |  |

| SEQBUFO3                                                        | Frame Buffer 03    | 0x13 | —              | —        | —           | —        | FRAMEBUFO3     | 0x00      |  |  |  |

| SEQBUFO4                                                        | Frame Buffer 04    | 0x14 | —              | —        | —           | —        | FRAMEBUFO4     | 0x00      |  |  |  |

| SEQBUFO5                                                        | Frame Buffer 05    | 0x15 | —              | —        | —           | —        | FRAMEBUFO5     | 0x00      |  |  |  |

| SEQBUFO6                                                        | Frame Buffer 06    | 0x16 | —              | —        | —           | —        | FRAMEBUFO6     | 0x00      |  |  |  |

| SEQBUFO7                                                        | Frame Buffer 07    | 0x17 | —              | —        | —           | —        | FRAMEBUFO7     | 0x00      |  |  |  |

| SEQBUFO8                                                        | Frame Buffer 08    | 0x18 | —              | —        | —           | —        | FRAMEBUFO8     | 0x00      |  |  |  |

| SEQBUFO9                                                        | Frame Buffer 09    | 0x19 | —              | —        | —           | —        | FRAMEBUFO9     | 0x00      |  |  |  |

| SEQBUFO10                                                       | Frame Buffer 10    | 0x1A | —              | —        | —           | —        | FRAMEBUFO10    | 0x00      |  |  |  |

| SEQBUFO11                                                       | Frame Buffer 11    | 0x1B | —              | —        | —           | —        | FRAMEBUFO11    | 0x00      |  |  |  |

| SEQBUFO12                                                       | Frame Buffer 12    | 0x1C | —              | —        | —           | —        | FRAMEBUFO12    | 0x00      |  |  |  |

| SEQBUFO13                                                       | Frame Buffer 13    | 0x1D | —              | —        | —           | —        | FRAMEBUFO13    | 0x00      |  |  |  |

| SEQBUFO14                                                       | Frame Buffer 14    | 0x1E | —              | —        | —           | —        | FRAMEBUFO14    | 0x00      |  |  |  |

| SEQBUFO15                                                       | Frame Buffer 15    | 0x1F | —              | —        | —           | —        | FRAMEBUFO15    | 0x00      |  |  |  |

| SEQBUFO16                                                       | Frame Buffer 16    | 0x20 | —              | —        | —           | —        | FRAMEBUFO16    | 0x00      |  |  |  |

| SEQBUFO17                                                       | Frame Buffer 17    | 0x21 | —              | —        | —           | —        | FRAMEBUFO17    | 0x00      |  |  |  |

| SEQBUFO18                                                       | Frame Buffer 18    | 0x22 | —              | —        | —           | —        | FRAMEBUFO18    | 0x00      |  |  |  |

| SEQBUFO19                                                       | Frame Buffer 19    | 0x23 | —              | —        | —           | —        | FRAMEBUFO19    | 0x00      |  |  |  |

| Capture Base 0xF400                                             |                    |      |                |          |             |          |                |           |  |  |  |

| PRESCALE                                                        | Pre-scale          | 0x00 | PRESCALE       |          |             |          |                | 0x00      |  |  |  |

| LPFSEL                                                          | Filter Num. Sel.   | 0x01 | CAP3LPF        | CAP2LPF  | CAP1LPF     | CAP0LPF  |                | 0x00      |  |  |  |

| MODE                                                            | Mode               | 0x02 | CAP3MODE       | CAP2MODE | CAP1MODE    | CAP0MODE |                | 0x00      |  |  |  |

| INTEN                                                           | Interrupt Enable   | 0x03 | CAP3OEN        | CAP3IEN  | CAP2OEN     | CAP2IEN  | CAP1OEN        | CAP1IEN   |  |  |  |

| CAPCTRL                                                         | CAP Control        | 0x04 | CAP3EN         | CAP2EN   | CAP1EN      | CAP0EN   | —              | —         |  |  |  |

| CAP0CNTL                                                        | CAP0 Counter Low   | 0x06 | CAP0CNTL       |          |             |          |                |           |  |  |  |

| CAP0CNTH                                                        | CAP0 Counter High  | 0x07 | CAP0CNTH       |          |             |          |                |           |  |  |  |

| CAP1CNTL                                                        | CAP1 Counter Low   | 0x08 | CAP1CNTL       |          |             |          |                |           |  |  |  |

| CAP1CNTH                                                        | CAP1 Counter High  | 0x09 | CAP1CNTH       |          |             |          |                |           |  |  |  |

| CAP2CNTL                                                        | CAP2 Counter Low   | 0x0A | CAP2CNTL       |          |             |          |                |           |  |  |  |

| CAP2CNTH                                                        | CAP2 Counter High  | 0x0B | CAP2CNTH       |          |             |          |                |           |  |  |  |

| CAP3CNTL                                                        | CAP3 Counter Low   | 0x0C | CAP3CNTL       |          |             |          |                |           |  |  |  |

| CAP3CNTH                                                        | CAP3 Counter High  | 0x0D | CAP3CNTH       |          |             |          |                |           |  |  |  |

| CAPINTF                                                         | CAP Interrupt Flag | 0x0F | CAP3OF         | CAP3F    | CAP2OF      | CAP2F    | CAP1OF         | CAP1F     |  |  |  |

| Timer 0 Base 0xF600 / Timer 1 Base 0xF800 / Timer 2 Base 0xFA00 |                    |      |                |          |             |          |                |           |  |  |  |

| INTEN                                                           | INT. Enable        | 0x00 | CH1EN3         | CH1EN2   | CH1EN1      | CH1ENO   | CHOIEN3        | CHOIEN2   |  |  |  |

| INTSTAT                                                         | INT. Status        | 0x01 | CH1INF3        | CH1INF2  | CH1INF1     | CH1INFO  | CHOINF3        | CHOINF2   |  |  |  |

| CHEN                                                            | Channel Enable     | 0x02 | CH1TEN3/CH1PEN | CH1TEN2  | CH1TEN1     | CH1TENO  | CHOTEN3/CHOPEN | CHOTEN2   |  |  |  |

| CHOCTRL                                                         | CH0 Control        | 0x03 | —              | —        | —           | PWMMPRK  | PWMMPOL        | CHMODE    |  |  |  |

| CH1CTRL                                                         | CH1 Control        | 0x04 | —              | —        | —           | PWMMPRK  | PWMMPOL        | CHMODE    |  |  |  |

| CHORLO                                                          | CH0 Reload 0       | 0x05 | CHORLO         |          |             |          |                |           |  |  |  |

| CHORL1                                                          | CH0 Reload 1       | 0x06 | CHORL1         |          |             |          |                |           |  |  |  |

| CHORL2                                                          | CH0 Reload 2       | 0x07 | CHORL2         |          |             |          |                |           |  |  |  |

| CHORL3                                                          | CH0 Reload 3       | 0x08 | CHORL3         |          |             |          |                |           |  |  |  |

| CH1RLO                                                          | CH1 Reload 0       | 0x09 | CH1RLO         |          |             |          |                |           |  |  |  |

| CH1RL1                                                          | CH1 Reload 1       | 0x0A | CH1RL1         |          |             |          |                |           |  |  |  |

| CH1RL2                                                          | CH1 Reload 2       | 0x0B | CH1RL2         |          |             |          |                |           |  |  |  |

| CH1RL3                                                          | CH1 Reload 3       | 0x0C | CH1RL3         |          |             |          |                |           |  |  |  |

| CHOCNTO                                                         | CH0 Counter 0      | 0x0D | CHOCNTO        |          |             |          |                |           |  |  |  |

| CHOCNT1                                                         | CH0 Counter 1      | 0x0E | CHOCNT1        |          |             |          |                |           |  |  |  |

| CHOCNT2                                                         | CH0 Counter 2      | 0x0F | CHOCNT2        |          |             |          |                |           |  |  |  |

| CHOCNT3                                                         | CH0 Counter 3      | 0x10 | CHOCNT3        |          |             |          |                |           |  |  |  |

| CH1CNT0                                                         | CH1 Counter 0      | 0x11 | CH1CNT0        |          |             |          |                |           |  |  |  |

| CH1CNT1                                                         | CH1 Counter 1      | 0x12 | CH1CNT1        |          |             |          |                |           |  |  |  |

| CH1CNT2                                                         | CH1 Counter 2      | 0x13 | CH1CNT2        |          |             |          |                |           |  |  |  |

| CH1CNT3                                                         | CH1 Counter 3      | 0x14 | CH1CNT3        |          |             |          |                |           |  |  |  |

| SPI Base 0xFC00                                                 |                    |      |                |          |             |          |                |           |  |  |  |

| TRNFMTO                                                         | Transfer Format 0  | 0x00 | —              | —        | —           | MOSIBID  | LSB            | SLV MODE  |  |  |  |

| TRNFM1                                                          | Transfer Format 1  | 0x01 | ADRLEN         |          | —           | DATLEN   |                |           |  |  |  |

| TRNCTRL0                                                        | Transfer Control 0 | 0x02 | RTRNCNT        |          |             |          |                |           |  |  |  |

| TRNCTRL1                                                        | Transfer Control 1 | 0x03 | WTRNCNT        |          |             | TOKENVU  | —              | —         |  |  |  |

| TRNCTRL2                                                        | Transfer Control 2 | 0x04 | —              | —        | TOKENEN     | WTRNCNT  |                |           |  |  |  |

| TRNCTRL3                                                        | Transfer Control 3 | 0x05 | —              | —        | ADREN       | —        | TRNCNT         |           |  |  |  |

| SPICMD                                                          | SPI Command        | 0x06 | CMD            |          |             |          |                |           |  |  |  |

| SPIADRO                                                         | SPI Address 0      | 0x07 | SPIADRO        |          |             |          |                |           |  |  |  |

| SPIADR1                                                         | SPI Address 1      | 0x08 | SPIADR1        |          |             |          |                |           |  |  |  |

| SPIADR2                                                         | SPI Address 2      | 0x09 | SPIADR2        |          |             |          |                |           |  |  |  |

| SPIDATA                                                         | SPI Data           | 0x0A | SPIDAT         |          |             |          |                |           |  |  |  |

| SPICTRLO                                                        | SPI Control 0      | 0x0B | —              | —        | —           | —        | TFIFORST       | RFIFORST  |  |  |  |

| SPICTRL1                                                        | SPI Control 1      | 0x0C | —              | —        | —           | —        | SPIIRST        |           |  |  |  |

| SPICTRL2                                                        | SPI Control 2      | 0x0D | —              | —        | —           | —        | RTHRCV         |           |  |  |  |

| SPISTATO                                                        | SPI Status 0       | 0x0E | —              | —        | —           | —        | TTHTRN         |           |  |  |  |

| SPISTAT1                                                        | SPI Status 1       | 0x0F | RFUL           | REMP     | —           | RFIFONUM |                |           |  |  |  |

| SPISTAT2                                                        | SPI Status 2       | 0x10 | TFUL           | TEMP     | —           | TFIFONUM |                |           |  |  |  |

| INTEN                                                           | INT. Enable        | 0x11 | —              | —        | SLVCMDIEN   | ENDTEN   | TFIFOEN        | RFIFOEN   |  |  |  |

| INTSTAT                                                         | INT. Status        | 0x12 | —              | —        | SLVCMDFINTF | ENDTINTF | TFIFOINTF      | RFIFOINTF |  |  |  |

| INTFTIM0                                                        | Interface Timing 0 | 0x13 | SCLKDIV        |          |             |          |                |           |  |  |  |

| INTFTIM1                                                        | Interface Timing 1 | 0x14 | —              | —        | CS2CLK      | CSHT     |                |           |  |  |  |

| SLVSTAT0                                                        | Slave Status 0     | 0x15 | USERSTAT0      |          |             |          |                |           |  |  |  |

| SLVSTAT1                                                        | Slave Status 1     | 0x16 | USERSTAT1      |          |             |          |                |           |  |  |  |

| SLVSTAT2                                                        | Slave Status 2     | 0x17 | —              | —        | —           | —        | URRUN          | ORRUN     |  |  |  |

| RCVCNT0                                                         | Recev. Counter 0   | 0x18 | RCVCNTL        |          |             |          |                |           |  |  |  |

| RCVCNT1                                                         | Recev. Counter 1   | 0x19 | —              | —        | —           | —        | —              | RCVCNTH   |  |  |  |

| TSMCNT0                                                         | Trans. Counter 0   | 0x1A | TRNCNTL        |          |             |          |                |           |  |  |  |

| TSMCNT1                                                         | Trans. Counter 1   | 0x1B | —              | —        | —           | —        | —              | TRNCNTH   |  |  |  |

| SPICFG                                                          | SPI Configuration  | 0x1C | —              | —        | TFIFOSIZE   | —        | —              | RFIFOSIZE |  |  |  |

| Multi-Function ALU Base 0xFE00 |                  |      |   |   |   |   |   |   |   |      |      |  |

|--------------------------------|------------------|------|---|---|---|---|---|---|---|------|------|--|

| MULCTRL                        | Multiply Control | 0x00 | - | - | - | - | - | - | - | SIGN | 0x00 |  |

|          |                    |      |               |   |   |   |       |      |

|----------|--------------------|------|---------------|---|---|---|-------|------|

| MULPO    | Multiplier 0       | 0x01 | MULTIPLIER0   |   |   |   |       | 0x00 |

| MULP1    | Multiplier 1       | 0x02 | MULTIPLIER1   |   |   |   |       | 0x00 |

| MULCO    | Multiplicand 0     | 0x03 | MULTIPLICAND0 |   |   |   |       | 0x00 |

| MULC1    | Multiplicand 1     | 0x04 | MULTIPLICAND1 |   |   |   |       | 0x00 |

| MULPROD0 | Multiply Product 0 | 0x05 | MULPRODUCT0   |   |   |   |       | 0x00 |

| MULPROD1 | Multiply Product 1 | 0x06 | MULPRODUCT1   |   |   |   |       | 0x00 |

| MULPROD2 | Multiply Product 2 | 0x07 | MULPRODUCT2   |   |   |   |       | 0x00 |

| MULPROD3 | Multiply Product 3 | 0x08 | MULPRODUCT3   |   |   |   |       | 0x00 |

| FPCTRL   | FP. Control        | 0x09 | —             | — | — | — | ROUND | 0x00 |

| FPMULPO  | FP. Multiplier 0   | 0x0A | FPMULTIPLIER0 |   |   |   |       | 0x00 |

| FPMULP1  | FP. Multiplier 1   | 0x0B | FPMULTIPLIER1 |   |   |   |       | 0x00 |

| FPMULP2  | FP. Multiplier 2   | 0x0C | FPMULTIPLIER2 |   |   |   |       | 0x00 |

| FPMULP3  | FP. Multiplier 3   | 0x0D | FPMULTIPLIER3 |   |   |   |       | 0x00 |

| FPMULC0  | FP. Multiplicand 0 | 0x0E | FPMULTICAND0  |   |   |   |       | 0x00 |

| FPMULC1  | FP. Multiplicand 1 | 0x0F | FPMULTICAND1  |   |   |   |       | 0x00 |

| FPMULC2  | FP. Multiplicand 2 | 0x10 | FPMULTICAND2  |   |   |   |       | 0x00 |

| FPMULC3  | FP. Multiplicand 3 | 0x11 | FPMULTICAND3  |   |   |   |       | 0x00 |

| FPPROD0  | FP. Mul. Product 0 | 0x12 | FPMULPRODUCT0 |   |   |   |       | 0x00 |

| FPPROD1  | FP. Mul. Product 1 | 0x13 | FPMULPRODUCT1 |   |   |   |       | 0x00 |

| FPPROD2  | FP. Mul. Product 2 | 0x14 | FPMULPRODUCT2 |   |   |   |       | 0x00 |

| FPPROD3  | FP. Mul. Product 3 | 0x15 | FPMULPRODUCT3 |   |   |   |       | 0x00 |

| FPSTAT   | FP. Status         | 0x16 | FPSTAT        |   |   |   |       | 0x00 |

| LOGIN0   | Log2 Input 0       | 0x17 | LOGINPUT0     |   |   |   |       | 0x00 |

| LOGIN1   | Log2 Input 1       | 0x18 | LOGINPUT1     |   |   |   |       | 0x00 |

| LOGIN2   | Log2 Input 2       | 0x19 | LOGINPUT2     |   |   |   |       | 0x00 |

| LOGIN3   | Log2 Input 3       | 0x1A | LOGINPUT3     |   |   |   |       | 0x00 |

| LOGOUT0  | Log2 Output 0      | 0x1B | LOGOUTPUT0    |   |   |   |       | 0x00 |

| LOGOUT1  | Log2 Output 1      | 0x1C | LOGOUTPUT1    |   |   |   |       | 0x00 |

| LOGOUT2  | Log2 Output 2      | 0x1D | LOGOUTPUT2    |   |   |   |       | 0x00 |

| LOGOUT3  | Log2 Output 3      | 0x1E | LOGOUTPUT3    |   |   |   |       | 0x00 |

| LOGSTAT  | Log2 Status        | 0x1F | LOGSTAT       |   |   |   |       | 0x00 |

Table 6.2-2 FE81 Series Peripheral Register Map Table

### **6.3 External Vectored Interrupt Controller (EVIC)**

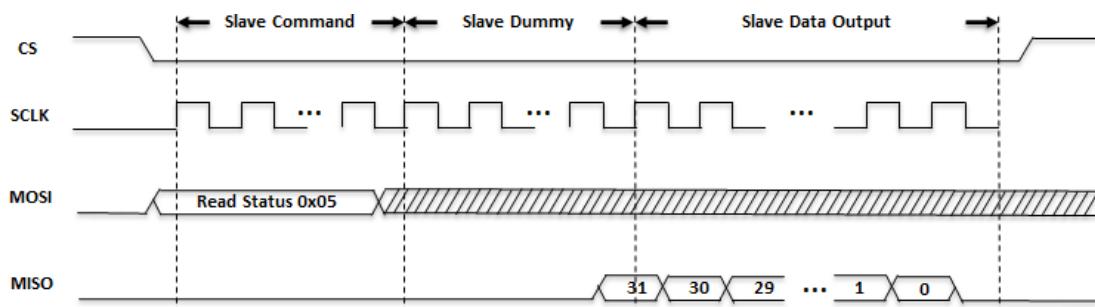

#### **6.3.1 Overview**